COMPARE MODE USING TIMER 1

- (, PRIVE A PIN HIGH OR LOW AT A

PRECISE TIME

a) SET TIMER COUNT TO REGUIRED TIME

b) SET OUTPUT TO OUT PIN RC2

TRISC(2) = 0

- C) SET REGISTER CCPICON (3:0) = 10002 SET OUTPUT ON MATCH

- d) EMABLE TIMER! AND OPERATION 15 AUTOMATIC

TIMER 1

TIMER 1

MATCH

2, PUT OUT A TIMES PULSE (PEATMAN)

PLOS)

# OUTPUT COMPARE

- (PUTY CYCLE = 50%)

- GENERATE PULSES

- GENERATE TIME DELAYS

- GENERATE PERMINIC INTERRUPTS

EXAMPLE PERLODIC INTERRUPTS

- AND FIRE SCR OR TRIAC

- WHEN Vin EVERY IMS AND AND WHEN Vin (thi) CD, CROSSING

NOW APPLY POWER - SEE CIRCUIT DIAGRAM

2. REAL TIME CLOCK - INCREMENT

VARIABLE WITH EACH INTERRUP

TO GET HOURS / MIN | SEC,

(THE PK 24FV304 HAS A RTC)

## 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 35. "Output Compare with Dedicated Timer" (DS39723).

All devices in the PIC24FV32KA304 family feature 3 independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events. Also, the modules can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 21 user-selectable trigger/sync sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

#### 15.1 General Operating Modes

## 15.1.1 SYNCHRONOUS AND TRIGGER MODES

By default, the output compare module operates in a free-running mode. The internal 16-bit counter, OCxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow, with its period synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-running mode is selected by default, or any time that the SYNCSEL bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSEL bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode. Setting this bit selects Trigger mode operation. In both modes, the SYNCSEL bits determine the sync/trigger source.

#### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase the range, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd-numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even-numbered module (OCy) provides the Most Significant 16 bits. Wrap arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules.

#### 15.2 Compare Operations

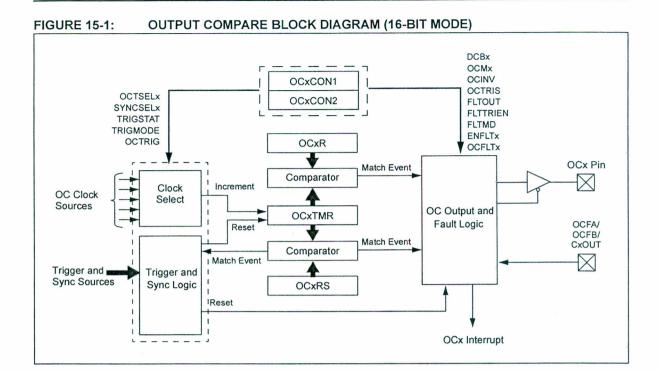

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width, and the time to the rising edge of the pulse.

- 2. Write the rising edge value to OCxR and the falling edge value to OCxRs.

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSEL bits to '00000' (no sync/trigger source).

- 5. Select the time base source with the OCTSEL<2:0> bits. If the desired clock source is running, set the OCTSEL<2:0> bits before the output compare module is enabled for proper synchronization with the desired clock source. If necessary, set the TON bit for the selected timer which enables the compare time base to count. Synchronous mode operation starts as soon as the synchronization source is enabled; Trigger mode operation starts after a trigger source event occurs.

- Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

For 32-bit cascaded operation, these steps are also necessary:

- Set the OC32 bits for both registers (OCyCON2<8> and (OCxCON2<8>). Enable the even-numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2), so the module will run in Synchronous mode.

- Configure the desired output and Fault settings for OCv.

- Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGSTAT (OCxCON2<6>) and SYNCSEL (OCxCON2<4:0>) bits.

- Configure the desired Compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx

Depending on the output mode selected, the module holds the OCx pin in its default state and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes and after each OCxRS match in Double Compare modes.

Single-shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

TABLE 4-8: OUTPUT COMPARE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14         | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6    | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|--------|----------------|----------|---------|---------|---------|--------|--------|--------|----------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1   | 0190 | -      | -              | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 | ENFLT0 | OCFLT2   | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | ОСМО     | 0000          |

| OC1CON2   | 0192 | FLTMD  | FLTOUT         | FLTTRIEN | OCINV   |         | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS     | 0194 |        | OC1RS          |          |         |         |         |        |        |        |          |        |          |          |          |          |          | 0000          |

| OC1R      | 0196 |        | OC1R           |          |         |         |         |        |        |        |          |        |          |          |          |          |          | 0000          |

| OC1TMR    | 0198 |        | OC1TMR         |          |         |         |         |        |        |        |          |        |          |          |          |          |          | xxxx          |

| OC2CON1   | 019A |        | 3 <del>1</del> | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 | ENFLT0 | OCFLT2   | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | ОСМО     | 0000          |

| OC2CON2   | 019C | FLTMD  | FLTOUT         | FLTTRIEN | OCINV   | - 3     | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS     | 019E |        | OC2RS          |          |         |         |         |        |        |        |          |        |          |          |          |          |          | 0000          |

| OC2R      | 01A0 |        | OC2R           |          |         |         |         |        |        |        |          |        |          |          |          |          |          | 0000          |

| OC2TMR    | 01A2 |        | OC2TMR         |          |         |         |         |        |        |        |          |        |          |          |          |          |          | xxxx          |

| OC3CON1   | 01A4 |        | _              | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1 | ENFLT0 | OCFLT2   | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | ОСМО     | 0000          |

| OC3CON2   | 01A6 | FLTMD  | FLTOUT         | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32   | OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS     | 01A8 |        |                |          |         |         |         |        |        | OC3RS  |          |        |          |          |          |          |          | 0000          |

| OC3R      | 01AA |        |                |          |         |         |         |        |        | OC3R   |          |        |          |          |          |          |          | 0000          |

| OC3TMR    | 01AC |        |                |          |         |         |         |        |        | OC3TMR |          |        |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.