Copyright

by

Isaac Westby

2020

# FPGA ACCELERATION ON MULTILAYER PERCEPTRON (MLP) NEURAL NETWORK FOR HANDWRITTEN DIGIT RECOGNTION

by

Isaac Westby, BS Electrical Engineering

## THESIS

Presented to the Faculty of

The University of Houston-Clear Lake

In Partial Fulfillment

Of the Requirements

For the Degree

MASTER OF SCIENCE

in Computer Engineering

THE UNIVERSITY OF HOUSTON-CLEAR LAKE

May 2020

# **Dedication**

I would like to dedicate this thesis to my Dad, thank you for all your love and support through the years.

# Acknowledgements

I would like to thank Dr. Xiaokun Yang for all his help on this project. I would like to thank him for being so helpful and understanding through the entire time. Without his support I would not have been able to accomplish all that I have in this project.

#### **ABSTRACT**

# FPGA ACCELERATION ON MULTILAYER PERCEPTRON (MLP) NEURAL NETWORK FOR HANDWRITTEN DIGIT RECOGNITION

Isaac Westby University of Houston-Clear Lake, 2020

Thesis Chair: Xiaokun Yang, PhD

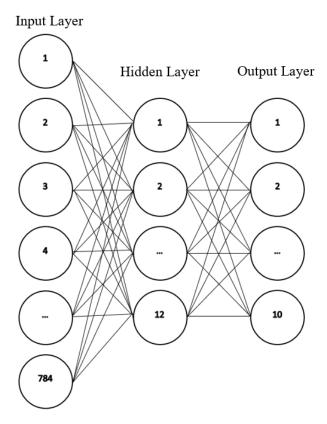

This dissertation presents a hardware implementation of a Multi-Layer Perceptron (MLP) network used for the purpose of low-latency, high-accuracy digit recognition. The accuracy of various network designs was compared in Python, and the final network design was comprised of 784 input neurons, a single hidden-layer of 12 neurons, and an output layer of 10 neurons. The weights and biases of this network were then trained using the Modified National Institute of Standards and Technology (MNIST) handwritten digit data in Python using the stochastic gradient descent method. This network design was then tested in software for the digit recognition accuracy of half (16-bit), single (32-bit), and double (64-bit) precision inputs. These all gave nearly the same results of (93.26, 93.25, and 93.25%) digit recognition accuracy respectively. This design was then implemented in hardware using the Verilog Hardware Description Language (HDL). This novel design uses a custom timing structure along with single-precision, floating-point

vi

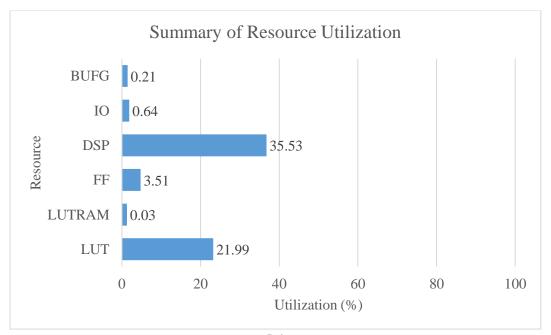

IPs from Vivado for multiplication, addition, subtraction, accumulation, exponential, and reciprocal. Results show a speedup of 40.3967 over the fastest software execution, and 127.219 over the slowest software execution. The results of the synthesis were found for the Kintex-Ultrascale FPGA, part xcku035-sfva784-1LV-I. These results showed a utilization of 44,668 Look Up Tables (LUT), 14,274 Flip Flops (FF), and 604 Digital Signal Processors (DSP), for utilization of 21.99%, 3.51%, and 35.53% respectively. Compared with related works, our proposed work provides the lowest latency for digit recognition, with a speedup of 61 and 42 over these works. Further compared to these related works, our design is between the two in accuracy and resource utilization, showing a tradeoff between design complexity and digit recognition accuracy. Conclusions of our research are that our proposed design presents a high-accuracy, low-latency digit recognition network. Our proposed design allows for further customization to fit with a future user's needs.

# TABLE OF CONTENTS

| List of Tables                                            | X  |

|-----------------------------------------------------------|----|

| List of Figures                                           | xi |

| CHAPTER 1: INTRODUCTION                                   | 1  |

| 1.1 Background                                            | 1  |

| 1.2 Related Works                                         | 2  |

| 1.3 Design Process                                        | 4  |

| 1.4 Structure of Dissertation                             | 4  |

| CHAPTER 2: PROPOSED DESIGN OF THE NETWORK                 | 6  |

| 2.1 Neural Networks                                       | 6  |

| 2.2 Sigmoid Neurons                                       |    |

| 2.3 Training the Neural Network                           |    |

| 2.4 Running the Python Code                               |    |

| 2.4.1 Resources Needed                                    | 10 |

| 2.4.2 Steps to Run the Code                               | 10 |

| 2.4.3 Exporting Weights and Biases to CSV                 | 13 |

| 2.5 Finding the Best Design                               |    |

| 2.5.1 Comparing Different Networks                        |    |

| 2.5.2 Adjusting Epoch, mini_batch_size, and Learning Rate | 18 |

| 2.6 Final Network Design                                  | 22 |

| CHAPTER 3: SOFTWARE IMPLEMENTATION                        | 24 |

| 3.1 Matlab Implementation                                 | 24 |

| 3.2 Matlab Results                                        |    |

| 3.3 Accuracy Comparison                                   | 32 |

| CHAPTER 4: HARDWARE IMPLEMENTATION                        | 34 |

| 4.1 Hardware Design Architecture                          | 34 |

| 4.2 Final Hardware Architecture                           | 39 |

| 4.3 Timing and RTL Design                                 | 40 |

| 4.3.1 How the Counters are Used                           | 40 |

| 4.3.2 RTL Design                                          | 44 |

| 4.4 Vivado IPs                                            |    |

| 4.4.1 Instantiating the IPs                               | 46 |

| 4.4.2 Distributed Memory Generator IP                     | 49 |

| 4.4.3 How to Create COE files Using Matlab                | 50 |

| 4.5 Running the Project                                   | 51 |

| 4.5.1 Creating the Project Using TCL    | 52 |

|-----------------------------------------|----|

| 4.5.2 Running the TCL Script            |    |

| 4.5.3 Synthesis in Vivado               |    |

| 4.5.4 Generating the Waveform in Vivado |    |

| 4.5.5 Interpreting Results in Vivado    |    |

| CHAPTER 5: RESULTS                      | 63 |

| 5.1 Execution Time on FPGA              | 63 |

| 5.2 Resource Cost on FPGA               | 64 |

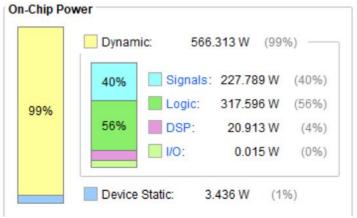

| 5.3 Power Cost on FPGA                  | 66 |

| 5.4 Comparison to Related Works         | 68 |

| 5.4.1 Accuracy Comparison               |    |

| 5.4.2 Speed Comparison                  | 68 |

| 5.4.3 Utilization Comparison            |    |

| 5.4.4 Summary of Comparison             |    |

| CHAPTER 6: CONCLUSIONS AND FUTURE WORK  | 71 |

| 6.1 Conclusions                         | 71 |

| 6.2 Future Work                         | 72 |

| REFERENCES                              | 74 |

| VITA ISAAC WESTRY                       | 81 |

# LIST OF TABLES

| Table 2.1 The data corresponding to graph in figure 2.4.                                                                         | 16 |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2 The data corresponding to graph in figure 2.5                                                                          | 17 |

| Table 3.1 A layout of the weights of the first hidden layer.                                                                     | 24 |

| Table 3.2 A layout of the input pixels of the first hidden layer.                                                                | 25 |

| Table 3.3 A layout of the biases of the first hidden layer.                                                                      | 25 |

| Table 3.4 An example layout of the weights1.csv file                                                                             | 26 |

| Table 3.5 An example layout output neuron biases.                                                                                | 26 |

| Table 3.6 Corresponding data used for comparison of 'strength' of single and double precision datatypes.                         | 30 |

| Table 3.7 Corresponding data used for comparison of 'strength' greater than 0.9 of single and double precision datatypes.        | 31 |

| Table 4.1 A comparison of the resources needed for a pipelined vs non-pipelined design.                                          | 36 |

| Table 4.2 A comparison of the resources needed for a pipelined, non-pipelined design, and pipelined with 98 multipliers designs. | 38 |

| Table 4.3 A table showing the results of the network with an input of a handwritten 7.                                           | 58 |

| Table 4.4 A table showing the results of the network with an input of a handwritten 2.                                           | 60 |

| Table 4.5 A table showing the results of the network with an input of a handwritten 1.                                           | 62 |

| Table 5.1 A comparison of the execution times in software and hardware                                                           | 64 |

| Table 5.2 The utilization results of the hardware synthesis                                                                      | 65 |

| Table 5.3 A further breakdown of the utilization results.                                                                        | 66 |

| Table 5.4 Accuracy comparison to related works                                                                                   | 68 |

| Table 5.5 Speed comparison to related works.                                                                                     | 69 |

| Table 5.6 A utilization comparison to related works                                                                              | 69 |

# LIST OF FIGURES

| Figure 2.1 A visualization of the Gradient descent curve.                                                                        | 9  |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 The output that you should see when running the Python code                                                           | 12 |

| Figure 2.3 An image showing the commands to save the weights and biases to a CSV file.                                           | 13 |

| Figure 2.4 A graph comparing accuracy of different networks with 1 hidden-layer of various numbers of neurons.                   | 15 |

| Figure 2.5 A graph comparing accuracy of different networks with 2 hidden-layers of various numbers of neurons.                  | 17 |

| Figure 2.6 A graph comparing networks with a single hidden layer and two hidden layers.                                          | 18 |

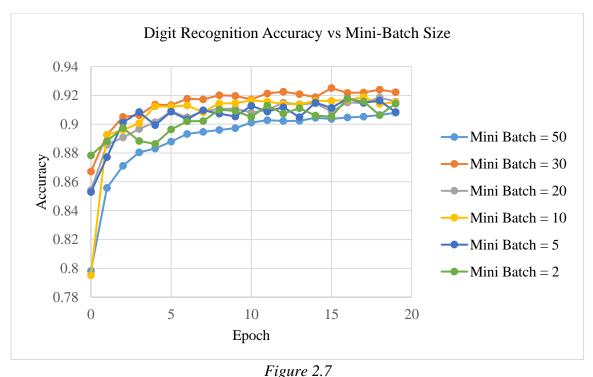

| Figure 2.7 A graph comparing the digit recognition accuracy with the mini-batch size.                                            | 19 |

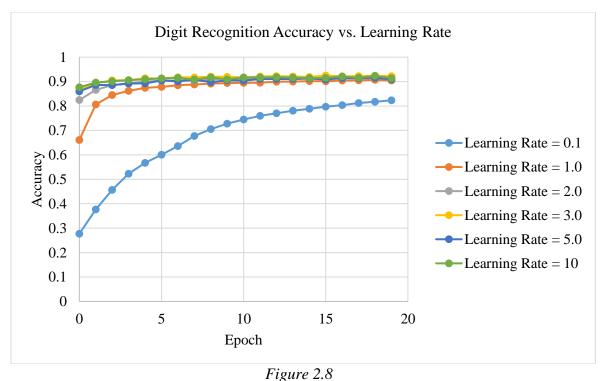

| Figure 2.8 A graph comparing the digit recognition accuracy with the learning rate                                               | 20 |

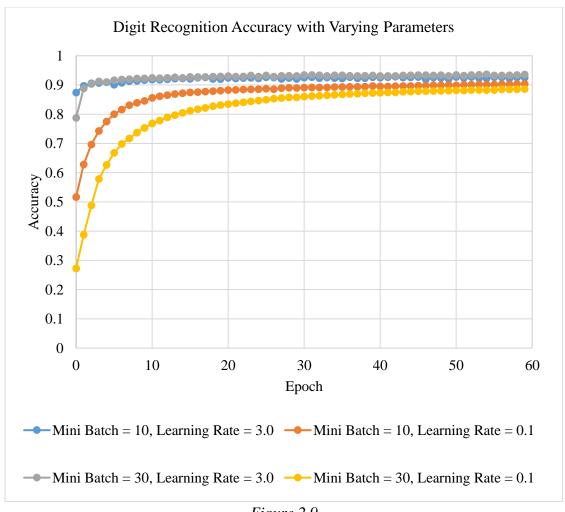

| Figure 2.9 A graph comparing the digit recognition accuracy with varying parameters.                                             | 21 |

| Figure 2.10 A figure showing the final network design.                                                                           | 23 |

| Figure 3.1 An example output when running the program                                                                            | 27 |

| Figure 3.2 An example output when running the program with an input of 3                                                         | 28 |

| Figure 3.3 Comparison of half, single, and double precision results in Matlab                                                    | 29 |

| Figure 3.4 Comparison of the 'strength' of single and double precision data-types                                                | 30 |

| Figure 3.5 Further comparison of the 'strength' greater than 0.9 of single and double precision data-types                       | 31 |

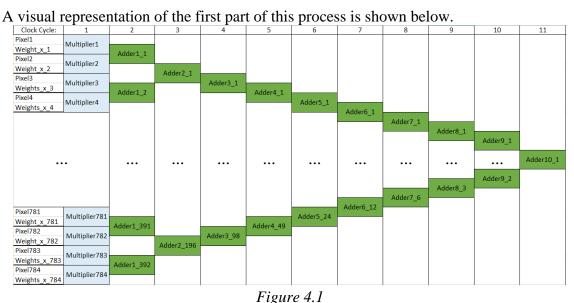

| Figure 4.1 A visual representation of the multipliers and adders going into the first layer hidden neurons.                      | 34 |

| Figure 4.2 A visual representation of the results from the multipliers and adders going into the final operations of the neuron. | 35 |

| Figure 4.3 A visual representation of the operations of a single output layer neuron.                                            | 36 |

| Figure 4.4 A visual representation of the first stage multiplication with 98 multipliers.                                        | 37 |

| Figure 4.5 A visual representation of the accumulation and final operations used after the 98 multipliers.                       | 38 |

|                                                                                                 | 39 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 4.6 A visual representation of all the components of the design put together.            | 39 |

| Figure 4.7 A visual diagram of the timing of operations aligned with counters                   | 43 |

| Figure 4.8 A simplified hardware translation of the enable design.                              | 45 |

| Figure 4.9 An example COE file for the hidden layer biases.                                     | 50 |

| Figure 4.10 The line in the .tcl file that needs to be changed to correspond to your directory. | 52 |

| Figure 4.11 An example of the direct path that needs to be changed                              | 53 |

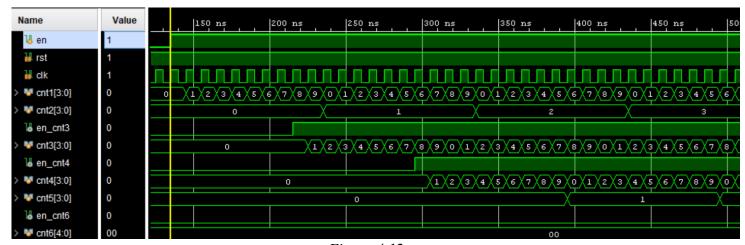

| Figure 4.12 Vivado waveform with all counters and their corresponding enable signals.           | 55 |

| Figure 4.13 Vivado waveform showing when cnt6 starts counting                                   | 56 |

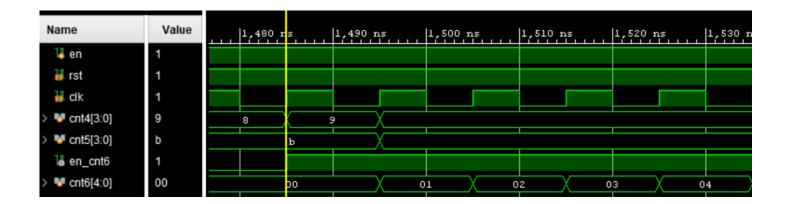

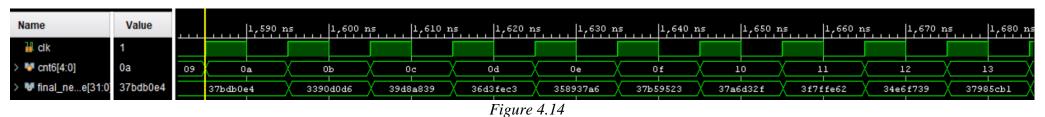

| Figure 4.14 Vivado waveform showing the final results of the network                            | 57 |

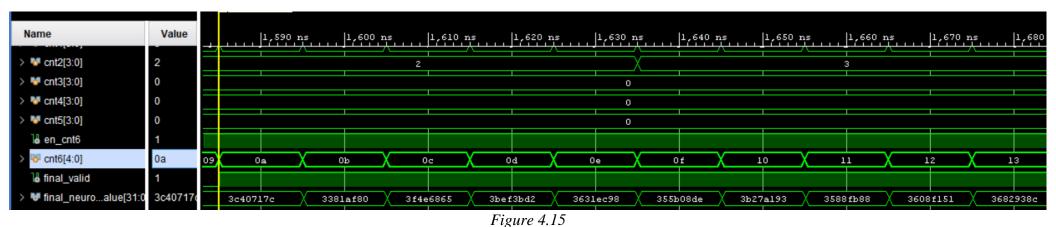

| Figure 4.15 Vivado waveform showing the final results of the network for input of 2.            | 59 |

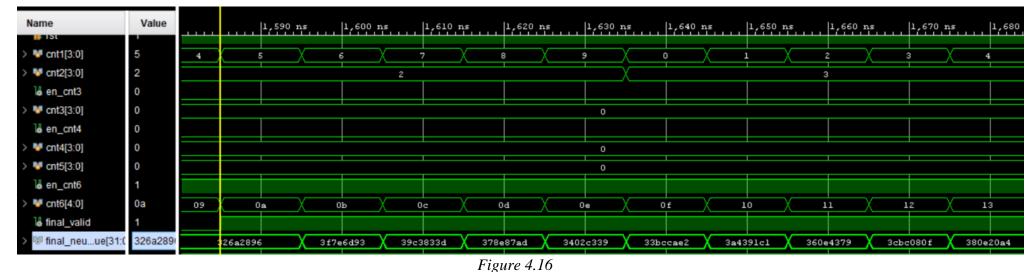

| Figure 4.16 Vivado waveform showing the final results of the network for input of 1.            | 61 |

| Figure 5.1 A graph of the utilization results.                                                  | 65 |

| Figure 5.2 An image of the power breakdown.                                                     | 67 |

| Figure 5.3 A further breakdown of the power consumption                                         | 67 |

#### CHAPTER 1:

#### **INTRODUCTION**

#### 1.1 Background

The subject of creating a computational model for neural networks (NNs) can be traced back to 1943 [45, 46]. Until 1970, the general method for automatic differentiation of discrete connected networks of nested differentiable functions has been published by Seppo Linnainmaa [47,48]. In 1980s, the VLSI technology enabled the development of practical artificial neural networks. A landmark publication in this field is a book authored by Carver A. Mead and Mohammed Ismail, titled "Analog VLSI Implementation of Neural Systems" in 1989 [49].

The real-world applications of NNs mainly appeared after 2000 [27]. In 2009, the design on the network with long short-term memory (LSTM) won three competitions of handwriting recognition without any prior knowledge about the three languages to be learned [52,53]. And in 2012, Ng and Dean created a network being able to recognize higher-level concepts such as cats [50].

Today, NNs have shown great ability to process emerging applications such as speech/music recognition [1,2], language recognition [3,33], image classification [4,5], video segmentation [6,19], and robotic [41, 43]. With the artificial intelligence (AI) chip market report published in May 2019, the global AI chip market size was valued at \$6,638.0 million in 2018, and is projected to reach \$91,185.1 million by 2025, growing at Compound Annual Growth Rate (CAGR) of 45.2% from 2019 to 2025 [54]. Therefore, to make NNs high speed and efficient will have a profound impact on transportation, sustainability, manufacturing, city services, banking, healthcare, education, entertainment, gaming, defense, criminal investigation, and many more.

Prior researches on NNs were mainly based on the software implementations, which can be very effective but require intensive CPU operations and memory bandwidth to achieve the desired results. The increasing computing power including but not limited to application-specific integrated circuit (ASIC), field-programmable gate array (FPGAs), and system-on-chips (SoCs) has been boosting the use of larger networks in image and visual recognition [23, 51]. These innovative technologies will contribute to making AI a reality, particularly to the time- and resource-constrained applications such as smart cars, industrial control systems, fraud detection with financial service, Internet of Medical Things (IoMT), speech recognition, natural language processing (NLP), automated speech recognition, and unmanned surveillance vehicles.

In addition, Internet of Things (IoT) devices have taken in data, processed it, and sent it off to the cloud where the results have been calculated, then these results are sent back to the IoT device [28,29,30]. This has been successful because the IoT device is able to remain simple, needing only to process and send off results. As the number of IoT device increases, and drives pressure on finite bandwidths, edge computing has emerged as a new trend [24, 40]. Edge computing allows for processing of data at the network edge rather than sending the data off and processing remotely. Software solutions are good up to a point, but hardware acceleration can provide a faster, lower power solution [31,32]. Under this context, in this paper a case study of the hardware acceleration on digit recognition with a FPGA is presented.

#### 1.2 Related Works

To date, many designs on digit recognition have been presented on the algorithm level [11,7] and hardware level [9,10,19]. For example, a recurrent neural network (RNN) has been proposed in [21] to recognize digits, and in [20] the designs on Deep

Neural Network (DNN), Convolutional neural networks) (CNN), and Bidirectional Recurrent Neural network (RNN) have been implemented and evaluated. As a result, the accuracy can reach 99.6% with the CNN and 97.8% with the four-layer DNN. The accuracy of RNN is 99.2%. All these researches were focused on exploring the accuracy of the implementations on algorithm and software level.

On hardware level, many prior researches focused on the design with high speed [22,8], low-energy cost [38,39,44], and security [36, 37]. In this thesis we concentrating on finding the optimal acceleration of digit recognition with FPGA corresponding to the quality edge. The latest implementation on multilayer perceptron (MLP) in [12] has shown the computation latency as 3.8 seconds including both training and inference. Four implementations were provided in this work, including four-bit, five-bit, six-bit, and eight-bit designs with FPGA. The eight-bit MLP consumed 34k logic elements but achieved the highest accuracy (89%) compared with the other implementations; and the four-bit design can reduce the slice count to 20k with 9% accuracy decrease. Different from the fully connected network as MLP, CNN is created with layers sparsely connected or partially connected. In [13], the digit recognition on an eight-bit CNN has been presented. Experimental results showed that the proposed hardware achieved a latency of 9.4 seconds on the design with sequential channel and 2.2 seconds with the parallel channel. The hardware costs are 20k and 98k respectively by using the sequential channel and parallel channel on FPGA. Both of the designs can achieve an accuracy over 90%. Compared with [12] and [13], a single-hidden-layer MLP is proposed to continually reduce the complexity of the design on digit recognition with FPGA.

#### 1.3 Design Process

The goal of this project was to design a neural network that could recognize handwritten digits with an accuracy of >90% and with a latency of < 3.5ms for each recognition. The implementation is based on the database of Modified National Institute of Standards and Technology (MNIST), which was developed by Yann LeCun, Corinna Cortes and Christopher Burges for evaluating machine learning models on the handwritten digit classification problem [15,14]. The network created was trained and tested based upon this MNIST data. The entire design process took place in a linear fashion and was composed of three major parts.

- 1. Decide on the network design to be used.

- 2. Test the network design in software using Matlab.

- 3. Build and test hardware implementation of the design in Vivado.

These are obviously simplified steps in the design process, but they reflect the major portions of the project. Each of these parts were internally iterative, (i.e. for step 1 various network designs were considered before a final one was chosen), but each step needed to be completed before moving on to the next.

#### 1.4 Structure of Dissertation

The remaining structure of the dissertation follows the parts of the design process through the completion of the project. In Chapter 2 I will be describing the proposed design of the network. In this chapter I will converge on a network design and describe how I reached this decision. In Chapter 3, I will be taking the proposed design described in Chapter 2, and implementing it in Matlab. This chapter will then compare the digit recognition accuracy of the network in Matlab using various floating-point precision inputs. Chapter 4 describes the hardware implementation and everything that went into

taking the design that was used in Matlab and converting it to RTL. Chapter 5 will then take the results of the hardware implementation and compare them to the results of the software implementation as well as to related works. Finally, in Chapter 6 the final conclusions of the project and future work are described.

#### CHAPTER 2:

#### PROPOSED DESIGN OF THE NETWORK

This chapter is important in showing the process of choosing network design that we did. We first cover some of the background on Neural Networks, then move onto discussing how the network is trained. Finally, Python code from [26] is used to setup and train the network is used to compare different networks with different training parameters.

#### 2.1 Neural Networks

The history of Neural Networks can be traced back to 1943 when McColluch and Pitts wrote a paper on how neurons work. In order to more easily explain this complex phenomenon, they used electrical circuits to show it [25]. It was with this previous work in mind, that the perceptron was created by Frank Rosenblatt. The perceptron takes in multiple binary inputs, and then outputs a single binary output. These inputs are then multiplied by their corresponding weights, and summed together. That sum is then compared to a bias value in order to determine the output of the neuron. The equation for the output of perceptron is shown.

$$output = \begin{cases} 0 & \text{if } \sum_{i} w_i * x_i + b \le 0 \\ 1 & \text{if } \sum_{i} w_i * x_i + b > 0 \end{cases}$$

where x is the input, x is the weight, and b is the bias.

This network design described by Rosenblatt gave us the ability to tweak or 'learn' new weights and biases in order to get the desired output. It is this idea that is the basis for most of the artificial neural networks that we see today.

#### 2.2 Sigmoid Neurons

The efficacy of the perceptron starts to break down when you are training it. Because the output is binary, any small change in the input weights and biases can affect the output. Due to the nature of the output being binary, it makes it very hard to 'train' these perceptron networks. This is where the sigmoid neuron comes in. The sigmoid neural network works similar to the perceptron network, except that the output is a value between 0 and 1.0, instead of a binary value of 0 or 1. The output for the sigmoid neuron is shown below.

sigmoid neuron output =

$$\frac{1}{1 + \exp(-(\sum_{i} w_i * x_i) + b)}$$

where w are the weights corresponding to the inputs x, and b represents the bias.

This sigmoid neuron solves the problem with training. By making small changes to the weights and biases of the sigmoid neuron, you are able to make small changes to the output, eventually converging on a 'correct' or most effective set of weights and biases.

Because of this fact, sigmoid neurons are used in the network that I am using. In order to simulate this network, I will need to run the sigmoid function for all neurons in the hidden and output layers. Also, to clarify a point of confusion here, as stated in [26], networks made up of sigmoid neurons are often referred to as Multi Layer Perceptron (MLP) networks. Any future reference to an MLP network is referring to a network made of these sigmoid neurons.

## 2.3 Training the Neural Network

As stated above, because we are using the sigmoid neuron in our network, we have the ability to train the network by making small changes to the weights and biases. In order to train our network, we are using the MNIST handwritten digit dataset. This

dataset has 60,000 handwritten digits with corresponding labels that can be used to train the network. There is then a separate set of 10,000 different handwritten digits with labels that can be used to test the network. The test data set also comes from a completely different group of people, so a person who drew a '2' for instance in the training set, will not have drawn any digits in the testing set.

The methods and ideas used in training the neural network are taken from the Neural Networks and Deep Learning Book by Michael Nielson [26]. In training the network, we have a cost function dependent on the weights and biases shown below.

$$C(w,b) \stackrel{\text{def}}{=} \frac{1}{2n} \sum_{x} \left| |y(x) - a| \right|^{2}$$

where y(x) is the results array of 10 values where the correct result has one value equal to 1 and the rest equal to 0. For example y(1) = (0, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0)T. The value of a represents the output vector of the network. The value of n is the total number of training inputs, and x is the value of the training input.

The idea here is that we want to minimize this cost function. This would mean that our results are as close as possible to y(x), which is the actual value. With this cost function, we are able to provide a result that is dependent on the two inputs (weights and biases) which are to be changed in training. The way that the Cost function is minimized is through the process of gradient descent. In this process, you are taking the gradient of the cost function repeatedly, such that with each step you are trying to decrease the Cost function the most. If we look at the image of the cost function, with two direction vectors from [26], shown on the next page.

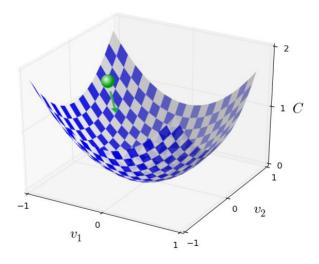

Figure 2.1 A visualization of the Gradient descent curve.

Looking at this image, the idea with gradient descent is to change the values of v1 and v2, that the green ball can 'roll' down to the minimum value of C. Through this gradient descent, we are updating the values for all the weights and biases. In order to compute the gradient for the cost function you need to compute the gradient of each individual function individually. This is a weak point of gradient descent when you have a large sample size used for training.

Stochastic Gradient descent is used as a way to speed up training. In this method we are doing the training based on a small random sample size, then average the entire thing together. This is different than calculating the entire gradient for all inputs in gradient descent method. In this training, we are choosing a 'mini-batch size' which is user defined and made up of randomly chosen inputs. The way that the training works is it choose a mini-batch of inputs and trains with those, once those have all been used, it then picks another mini-batch of inputs until all the inputs have been exhausted. Once all the inputs have been exhausted, this is called an 'Epoch'. Once an Epoch has been completed, the process starts all over again in the next Epoch. The analogy that is used in

[26] is to think of this like political polling, where we are just looking at a small sample size that is representative of the whole more or less. This process is implemented in the Python code provided by [26] and used for training my network.

## 2.4 Running the Python Code

#### 2.4.1 Resources Needed

In generating the weights and biases for the sigmoid Neural Network, Python was used. In my case, I have done this task using Python 2.7.17, which can be downloaded at https://www.python.org/downloads/release/python-2716/.

The code that is used to accomplish this task is written by [26] and can be found at https://github.com/mnielsen/neural-networks-and-deep-learning.

You can also clone the entire repository using the following command:

git clone https://github.com/mnielsen/neural-networks-and-deep-

learning.git

From this repository, the files that will be used are:

neural-networks-and-deep-learning/data/mnist.pkl.gz neural-networks-and-deep-learning/src/mnist\_loader.py neural-networks-and-deep-learning/src/network.py

These files also use a Python Library called Numpy, which can be downloaded at https://www.scipy.org/install.html .

### 2.4.2 Steps to Run the Code

To run the code to generate the weights and biases of a network of your design, follow these steps.

- 1. Move the above three files (mnist.pk.gz, mnist\_loader.py, and network.py) into your working Python directory. In my case, C:\Python27. Make sure you have installed Numpy into this directory if you did not already have it installed.

- 2. Open 'IDLE (Python GUI)'. This should open up a Python shell.

- 3. Execute the following in the python shell:

import mnist\_loader

This imports the helper file, mnist\_loader.py that unpacks the MNIST data.

4. Execute the following in the python shell: training\_data, validation\_data, test\_data = mnist\_loader.load\_data\_wrapper() This again is setting up the MNIST data that is used for training, validation, and testing.

5. Execute the following in the python shell:

import network

This imports the network python file.

6. Execute the following in the python shell:

net = network.Network([784, 30, 10])

This command is setting up the Neural Network that we are using here. The number of input neurons is 28-pixel x 28-pixel = 784. The hidden-layer neuron value here is 30, and the output layer neuron value is 10. The input and output layer values need to remain static, but the number of neurons in the hidden layer can be changed, as well as the number of hidden layers (i.e. [784, 30, 30, 10].

7. Execute the following in the python shell: net.SGD(training\_data, 30, 10, 3.0, test\_data=test\_data)

This command starts the training of the neural network by Stochastic Gradient Descent. The variables represent, the training data that is being used, the number of epochs over which it is trained (30), the mini-batch size used (10), the learning rate (3.0), and the test data being used.

Once the above steps have been completed, you should see an output similar to

#### below:

```

Python 2.7.17 Shell

File Edit Shell Debug Options Window Help

Python 2.7.17 (v2.7.17:c2f86d86e6, Oct 19 2019, 21:01:17) [MSC v.1500 64 bit (AMD64)] on win32

Type "help", "copyright", "credits" or "license()" for more information.

>>> import mnist loader

>>> training data, validation data, test data = mnist loader.load data wrapper()

>>> import network

>>> net = network.Network([784, 30, 10])

>>> net.SGD(training_data, 30, 10, 3.0, test_data=test_data)

Epoch 0: 8235 / 10000

Epoch 1: 8353 / 10000

Epoch 2: 8446 / 10000

Epoch 3: 8483 / 10000

Epoch 4: 8492 / 10000

Epoch 5: 8513 / 10000

Epoch 6: 8554 / 10000

Epoch 7: 8559 / 10000

Epoch 8: 9419 / 10000

Epoch 9: 9448 / 10000

Epoch 10: 9454 / 10000

Epoch 11: 9475 / 10000

Epoch 12: 9451 / 10000

Epoch 13: 9457 / 10000

Epoch 14: 9470 / 10000

Epoch 15: 9493 / 10000

Epoch 16: 9459 / 10000

Epoch 17: 9487 / 10000

Epoch 18: 9493 / 10000

Epoch 19: 9502 / 10000

Epoch 20: 9465 / 10000

Epoch 21: 9485 / 10000

Epoch 22: 9464 / 10000

Epoch 23: 9504 / 10000

Epoch 24: 9500 / 10000

Epoch 25: 9501 / 10000

Epoch 26: 9494 / 10000

Epoch 27: 9500 / 10000

Epoch 28: 9523 / 10000

Epoch 29: 9489 / 10000

>>>

```

Figure 2.2

The output that you should see when running the Python code.

The values here show the number of correct digit classifications were made across each epoch with the weights and biases. In order to design the most accurate Neural Network, the values of the neurons, epochs, mini-batch size, and learning rate can be changed in order to find the weights and biases that are for that design.

### 2.4.3 Exporting Weights and Biases to CSV

Once you are content with the design of the network and the accuracy, you can export the values of the weights and biases by running the following commands:

```

import numpy

numpy.savetxt("weights0.csv", net.weights[0], delimiter=",")

numpy.savetxt("weights1.csv", net.weights[1], delimiter=",")

numpy.savetxt("biases0.csv", net.biases[0], delimiter=",")

numpy.savetxt("biases1.csv", net.biases[1], delimiter=",")

```

In the Python shell it should look like below:

```

>>> import numpy

>>> numpy.savetxt("weights0.csv", net.weights[0], delimiter=",")

>>> numpy.savetxt("weights1.csv", net.weights[1], delimiter=",")

>>> numpy.savetxt("biases0.csv", net.biases[0], delimiter=",")

>>> numpy.savetxt("biases1.csv", net.biases[1], delimiter=",")

Figure 2.3

```

An image showing the commands to save the weights and biases to a CSV file.

Make sure that the quotation marks used match as shown in the above image, I had a problem with this when copying/pasting the commands.

After executing these commands, you will have four separate CSV files with the weights and biases for your network.

#### 2.5 Finding the Best Design

Once the method for finding the accuracy of the network with a trained set of weights and biases had been established, the goal was now to decide on a network design. In choosing the design, the goal was to have a high accuracy in digit detection, while maintaining as simple a design as possible.

In choosing the network design, there were a few things that would be forced to remain static due to the problem at hand. First, the input layer would require 784 neurons due to the fact that the MNIST digit images we would be using to train the network are 28-pixel × 28-pixel = 784 input pixels in size. The second thing that would need to remain static, is the fact there would be 10 output neurons. This value is static at 10 because there are 10 possible outputs (0-9) that would converge to a value of around 1 when that value is converged on by the network. The value of 10 outputs is chosen over a value of 4 outputs (24=16 possible outputs), because according to [26], the design of a system using 10 outputs rather than 4 produced empirically better results. This leaves the number of hidden layers, as well as the number of neurons in each hidden layer as the values that can be adjusted.

Once a network design (number of hidden layers and number of nodes in each layer) has been decided, the values of epochs used, mini\_batch\_size, and learning rate can be tweaked in order to find the best results. These values are static with values of epoch = 30, mini\_batch\_size = 10, and learning rate = 3.0, when comparing different network designs. Once a network design was chosen, these values were tweaked in order to find the most accurate set of weights and biases.

## 2.5.1 Comparing Different Networks

As stated above, various network designs were considered to find a network that would be able to be implemented with relative simplicity but still attain a high accuracy.

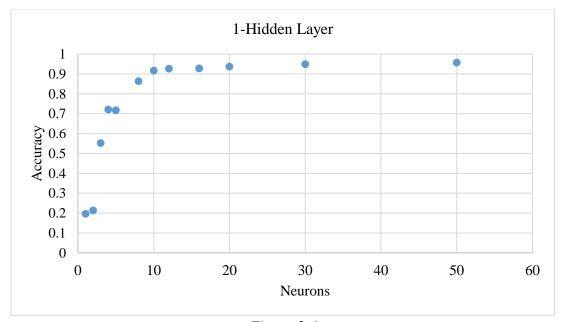

When testing different networks, the epoch, mini\_batch size, and learning rate all remained the same, but the number of hidden layers and neurons in each layer were changed. The following 1-hidden layer networks were tested [784, 50, 10], [784, 30, 10], [784, 20, 10], [784, 16, 10], [784, 12, 10], [784, 10, 10], [784, 8, 10], [784, 5, 10], [784, 4, 10], [784, 3, 10], [784, 2, 10], [784, 1, 10]. Where the first number is the input layer number, the second number is the number of neurons in the hidden layer, and the third number is the output layer neurons. The results are shown below.

Figure 2.4

A graph comparing accuracy of different networks with 1 hidden-layer of various numbers of neurons.

| Neurons | Accuracy |

|---------|----------|

| 50      | 0.9568   |

| 30      | 0.9489   |

| 20      | 0.9366   |

| 16      | 0.9277   |

| 12      | 0.9264   |

| 10      | 0.9167   |

| 8       | 0.8639   |

| 5       | 0.7176   |

| 4       | 0.7213   |

| 3       | 0.552    |

| 2       | 0.2132   |

| 1       | 0.1961   |

Table 2.1

The data corresponding to graph in figure 2.4.

The results of a network using 1-hidden layer show that as you increase the number of the neurons in the middle layer from 1 up, the output increases exponentially and asymptotically approaches a value of 1.0.

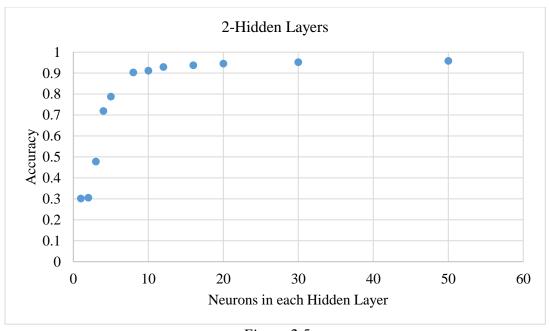

When using 2-hidden layers, the following networks were tested; [784, 50, 50, 10], [784, 30, 30, 10], [784, 20, 20, 10], [784, 16, 16, 10], [784, 12, 12, 10], [784, 10, 10, 10], [784, 8, 8, 10], [784, 5, 5, 10], [784, 4, 4, 10], [784, 3, 3, 10], [784, 2, 2, 10], [784, 1, 1, 10]. Again, the second and third numbers show the value of neurons used in the first and second hidden layers. The results are shown on the next page in figure 2.5.

Figure 2.5

A graph comparing accuracy of different networks with 2 hidden-layers of various numbers of neurons.

| Hidden Layer 1 | Hidden Layer 2 | Accuracy |

|----------------|----------------|----------|

| 50             | 50             | 0.9582   |

| 30             | 30             | 0.952    |

| 20             | 20             | 0.9453   |

| 16             | 16             | 0.9379   |

| 12             | 12             | 0.9296   |

| 10             | 10             | 0.9121   |

| 8              | 8              | 0.9032   |

| 5              | 5              | 0.7882   |

| 4              | 4              | 0.7194   |

| 3              | 3              | 0.4781   |

| 2              | 2              | 0.3055   |

| 1              | 1              | 0.3019   |

Table 2.2

The data corresponding to graph in figure 2.5.

The digit recognition accuracy results when using two hidden layers of the same size showed similar results to using one hidden layer. As you can see above, the accuracy increases in an exponential fashion when you add more neurons to each layer, then

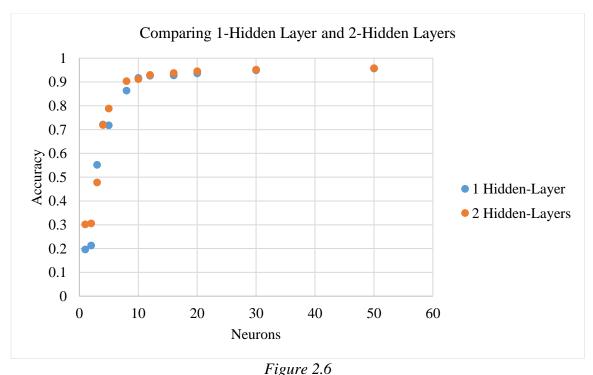

asymptotically approaches near 100% accuracy. Below I have included a graph comparing the digit recognition accuracy of the one hidden-layer and two hidden-layer networks described above. As seen for the results, the two-hidden layer networks edge out the single hidden-layer networks.

A graph comparing networks with a single hidden layer and two hidden layers.

For networks that have 10 neurons or greater in the hidden-layer(s), the difference in accuracy is especially small. This was taken into consideration when deciding the final network design.

## 2.5.2 Adjusting Epoch, mini\_batch\_size, and Learning Rate

With any network design, you can adjust the Epoch, mini\_batch\_size, and learning rate when training the network. These values are important to how quickly the network's weights and biases can be trained to the highest attainable digit recognition accuracy.

For my testing of these values, I used a network with 784 input-layer neurons, 12 hidden-layer neurons, and 10 output-layer neurons. I then set the Epoch = 20, learning rate = 3.0, then varied the mini\_batch\_size. The mini\_batch\_size is used to set the number size of the batches that are used to train the weights and biases. The result are shown below.

A graph comparing the digit recognition accuracy with the mini-batch size.

The results from changing the mini\_batch\_size showed that changes had a small effect on the overall digit recognition accuracy of the network after 20 epochs. Taking the results from above, I then tested changing the learning rate. For this case the values of mini\_batch\_size = 30 and epoch = 20.

A graph comparing the digit recognition accuracy with the learning rate.

The results here show that by changing the learning rate, the number of epochs it takes for the network to reach the perceived 'highest accuracy level' of around 92%, is mainly what is affected here. For these results there is virtually no discernible difference in the performance of training for learning rates between 2.0 - 10.

One final test was conducted using four different combinations across 60 epochs. The combinations used here were, mini\_batch\_size = 10 & learning rate = 3.0, mini\_batch\_size = 10 & learning rate = 0.1, mini\_batch\_size = 30 & learning rate = 3.0, and finally mini\_batch\_size = 30 & learning rate = 3.0. The results of this test are shown on the next page.

Figure 2.9 A graph comparing the digit recognition accuracy with varying parameters.

By testing these varying parameters, we are able to figure out which combination will lead to the most accurate set of weights and biases in the shortest amount of time. In my case, since the biases and weights are only going to be generated one time, then used in the network after that point, I can train the network for many more epoch, so that the accuracy can be as high as possible.

## 2.6 Final Network Design

As I stated before, when choosing the design of the network there were certain things that had be taken into consideration. We wanted to have an accuracy that would be greater than 90%, preferably a little higher, as well as simple as a design as possible. This would keep the resource and power costs down.

The first thing that would need to be figured out is how many hidden layers would be needed. As shown in section 2.5.1, various networks with one and two hidden layers were compared. These results showed that networks with two hidden layers performed better than networks with a singles hidden layer, but this increase was less than 1% in the case of the higher performing networks.

Once I had decided to only include a single hidden layer, I would now need to decide how many neurons would be in that layer. Again, the goal was to have greater than 90% accuracy, so I knew I would need at least 10 neurons in the hidden layer. A big consideration here was the need to reduce the number of neurons in order to make the design simpler in hardware. Each neuron would have to take as an input the 784 input neuron values multiplied by their respective weights. Each additional neuron would either add many floating-point adders, or additional cycles of latency to the system. Because of this tradeoff, I decided to go with 12 neurons in the hidden layer. This decision was made because at this number of neurons, each additional neuron does not add that much to the overall accuracy of the system. The final design of the network is shown in figure 2.10.

Figure 2.10 A figure showing the final network design.

Once a network design had been chosen, I could run the python program again to generate the final weights and biases that would be used. For this task, I used the techniques that were described in section 2.5.2, with Epoch = 60, mini\_batch\_size = 30, and Learning Rate = 3.0. There is a random nature to these numbers, so I ran this multiple times until I had a set of weights and biases that gave me an accuracy of 93.25%.

#### CHAPTER 3:

#### SOFTWARE IMPLEMENTATION

## 3.1 Matlab Implementation

Once a design had been chosen, the next step was to prove the approximate design with single precision floating-point numbers. This step is important in ensuring the weights and biases trained in Python work in my approximate design.

The implementation of the design begins with the weights and biases that were generated in Python. It is important to understand how the weights and biases are set up so that they can be correctly used in the network. The setup of weights0.csv is shown below. For this file we have a file with 9,408 single precision weights. These weights are distributed in 12 rows and 784 columns. Each row represents the weights associated with one of the 12 neurons in the hidden-layer.

| $w1_1$           | $w1_2$           | w1 <sub>3</sub>  | ••• | w1 <sub>783</sub>  | w1 <sub>784</sub>  |

|------------------|------------------|------------------|-----|--------------------|--------------------|

| $w2_1$           | $w2_2$           | w2 <sub>3</sub>  | ••• | w2 <sub>783</sub>  | w2 <sub>784</sub>  |

| $w3_1$           | w3 <sub>2</sub>  | $w3_3$           | ••• | w3 <sub>783</sub>  | w3 <sub>784</sub>  |

|                  |                  |                  |     |                    |                    |

| w11 <sub>1</sub> | w11 <sub>2</sub> | w11 <sub>3</sub> | ••• | w11 <sub>783</sub> | w11 <sub>784</sub> |

| w12 <sub>1</sub> | w12 <sub>2</sub> | w12 <sub>3</sub> |     | w12 <sub>783</sub> | w12 <sub>784</sub> |

Table 3.1 A layout of the weights of the first hidden layer.

The input image input into the network is a 28-pixel  $\times$  28-pixel grayscale image. The way that these pixels are numbered is shown in table 3.2 on the next page.

| $p_1$            | $p_2$            | <b>p</b> <sub>3</sub> | p <sub>4</sub>   | <br>p <sub>25</sub>  | p <sub>26</sub>  | p <sub>27</sub>  | p <sub>28</sub>  |

|------------------|------------------|-----------------------|------------------|----------------------|------------------|------------------|------------------|

| p <sub>29</sub>  | p <sub>30</sub>  | p <sub>31</sub>       | p <sub>32</sub>  | <br>p <sub>53</sub>  | p <sub>54</sub>  | p <sub>55</sub>  | p <sub>56</sub>  |

| p <sub>57</sub>  | p <sub>58</sub>  | p <sub>59</sub>       | p <sub>60</sub>  | <br>p <sub>81</sub>  | p <sub>82</sub>  | p <sub>83</sub>  | p <sub>84</sub>  |

|                  |                  |                       |                  | <br>                 |                  |                  |                  |

| p <sub>701</sub> | p <sub>702</sub> | p <sub>703</sub>      | p <sub>704</sub> | <br>p <sub>725</sub> | p <sub>726</sub> | p <sub>727</sub> | p <sub>728</sub> |

| p <sub>729</sub> | p <sub>730</sub> | p <sub>731</sub>      | p <sub>732</sub> | <br>p <sub>753</sub> | p <sub>754</sub> | p <sub>755</sub> | p <sub>756</sub> |

| p <sub>757</sub> | p <sub>758</sub> | p <sub>759</sub>      | p <sub>760</sub> | <br>p <sub>781</sub> | p <sub>782</sub> | p <sub>783</sub> | p <sub>784</sub> |

Table 3.2

A layout of the input pixels of the first hidden layer.

For the first hidden layer, in the file biases0.csv, there are 12 biases, one for each neuron. The setup of the file biases0.csv is shown below.

| $b_1$           |

|-----------------|

| $b_2$           |

| $b_3$           |

| •••             |

| $b_{10}$        |

| b <sub>11</sub> |

| $b_{12}$        |

Table 3.3

A layout of the biases of the first hidden layer.

The output for the hidden-layer neurons is then:

$$output(x) = \frac{1}{1 + \exp(-\sum_{i=1}^{784} w x_i * p_i - b_x)}$$

where in the above equation, i, refers to the input neuron, and the corresponding weight for that input, and x refers to the hidden layer neuron (1-12) that the output is being calculated for.

Once all 12 of the outputs of the hidden layer neurons are found, these values act as inputs to the 10 output layer neurons. A similar process in finding the outputs takes place as for the first hidden layer neurons, except this time we are using weights1.csv, and biases1.csv.

The file weights1.csv is laid out the same as weights0.csv, except this time there are 10 rows for the output neurons, and 12 columns for the inputs. An example of how the file is setup is shown below.

| $w1_1$           | w1 <sub>2</sub>  | w1 <sub>3</sub> | ••• | w1 <sub>11</sub>  | w1 <sub>12</sub> |

|------------------|------------------|-----------------|-----|-------------------|------------------|

| $w2_1$           | $w2_2$           | $w2_3$          |     | w2 <sub>11</sub>  | $w2_{12}$        |

| w3 <sub>1</sub>  | $w3_2$           | $w3_3$          | ••• | w3 <sub>11</sub>  | w3 <sub>12</sub> |

| • • •            | •••              | •••             | ••• | •••               | •••              |

| w9 <sub>1</sub>  | w9 <sub>2</sub>  | w9 <sub>3</sub> | ••• | w9 <sub>11</sub>  | w9 <sub>12</sub> |

| w10 <sub>1</sub> | w10 <sub>2</sub> | $w10_{3}$       | ••• | w10 <sub>11</sub> | $w10_{12}$       |

Table 3.4 An example layout of the weights1.csv file.

The file biases1.csv is similar to biases0.csv, except there are only 10 values (one for each output neuron). An example of how this file is setup is shown below.

| $b_1$          |

|----------------|

| $b_2$          |

| b <sub>3</sub> |

| • • •          |

| $b_8$          |

| b <sub>9</sub> |

| $b_{10}$       |

| Table 3.5      |

An example layout output neuron biases.

The output for the output layer neurons is then:

$$output(x) = \frac{1}{1 + \exp\left(-\sum_{i=1}^{12} wx_i * hidden\_out_i - b_x\right)}$$

where in the above equation, i, refers to the hidden layer neuron that is multiplied with corresponding, output of that neuron, hidden\_out. The value, x, refers to the output layer neuron (1-10) that the output is being calculated for.

The way the whole network fits together is an image is input into the network.

These 784 input values are used with the corresponding 9,408 weights, and 12 biases to

find the 12 outputs of the hidden layer neurons. The outputs of the hidden layer are then used with the corresponding 120 weights, and 10 biases to find the 10 outputs of the hidden layer neurons. Once this entire process has completed, the network has processed and classified one image.

The way the results are extrapolated from the neurons is simple. The output of each neuron is a value between 0 and 1.0. For each image, the network should converge on a single digit value. So the results for one neuron should be very close to 1.0 while the other values should be very close to 0. The neurons are assigned such that  $\operatorname{output}(1) = 0$ ,  $\operatorname{output}(2) = 1$ , ...,  $\operatorname{output}(10) = 9$ . An example output when running the program can be seen below.

An example output when running the program.

The way the program works is it goes through each value of the outputs (0-9) sequentially, and if the current value is greater than the previous, it sets the value for variable 'answer' equal to that number. That is why we see the output 'The answer is 1', when that number is processed, because the value for 1 (0.0001626174), is greater than the value for 0 (0.000000007). We can see for the number 6, we have a value of

0.9999223948. Because this number is the highest, we can determine that the network has processed the input image, and classified it as a '6'.

#### 3.2 Matlab Results

The implementation described above was run in Matlab using IEEE-754 double (64-bits), single (32-bits), and half (16-bits) precisions. The network was tested using the 10,000 MNIST test images. These are the same 10,000 images that were used to test the accuracy of the network in the Python program, and were not used in training the weights and biases.

In the first test, for each input image, all 10 of the outputs were compared and the highest value was determined to be the result. For instance, if we have the outputs shown below. The answer would be 3 even though the number for 3 (0.6894786954) isn't as strong as it could be (0.9999).

```

The outputted value for 0 = 0.0000003561

The answer is 0

The outputted value for 1 = 0.0000059766

The answer is 1

The outputted value for 2 = 0.0198363531

The answer is 2

The outputted value for 3 = 0.6894786954

The answer is 3

The outputted value for 4 = 0.0000000649

The outputted value for 5 = 0.0012522331

The outputted value for 6 = 0.0000001147

The outputted value for 7 = 0.0000000442

The outputted value for 9 = 0.00000994121

The outputted value for 9 = 0.00000465117

```

Figure 3.2

An example output when running the program with an input of 3.

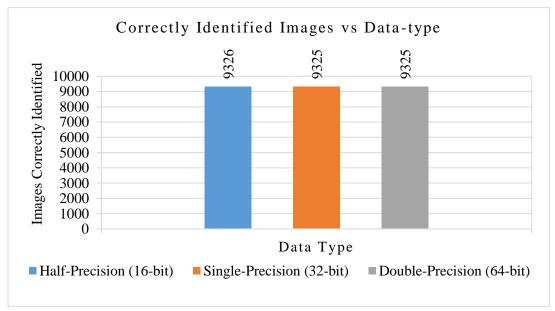

This test ran for all 10,000 of the MNIST test images. The results below show how many images were correctly identified for half, single, and double precision datatypes.

Figure 3.3

Comparison of half, single, and double precision results in Matlab.

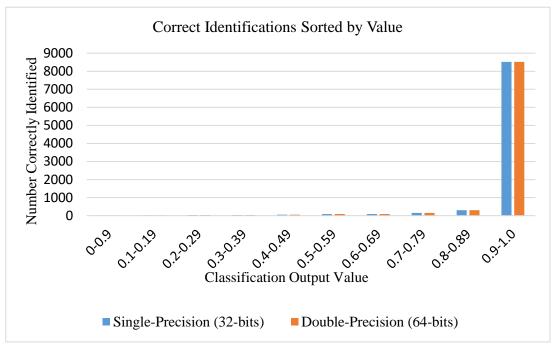

With each correct identification the value of the number that the network classified could be any value from 0 - 1.0. The number that is output from each neuron can be described as the 'strength' of the result. With a value of 1.0 meaning the network has classified that as being the result with the highest probability, and a value of 0 meaning that it has the lowest chance of being that value. In figure 3.4 is a graph that shows the 'strength' of the images that were classified correctly.

Figure 3.4 Comparison of the 'strength' of single and double precision data-types.

|                  | 0-  | 0.1- | 0.2- | 0.3- | 0.4- | 0.5- | 0.6- | 0.7- | 0.8- | 0.9- |

|------------------|-----|------|------|------|------|------|------|------|------|------|

|                  | 0.9 | 0.19 | 0.29 | 0.39 | 0.49 | 0.59 | 0.69 | 0.79 | 0.89 | 1.0  |

| Single-Precision |     |      |      |      |      |      |      |      |      |      |

| (32-bits)        | 14  | 19   | 36   | 36   | 57   | 91   | 89   | 155  | 304  | 8524 |

| Double-Precision |     |      |      |      |      |      |      |      |      |      |

| (64-bits)        | 14  | 19   | 36   | 36   | 57   | 91   | 89   | 155  | 304  | 8524 |

Table 3.6

Corresponding data used for comparison of 'strength' of single and double precision datatypes.

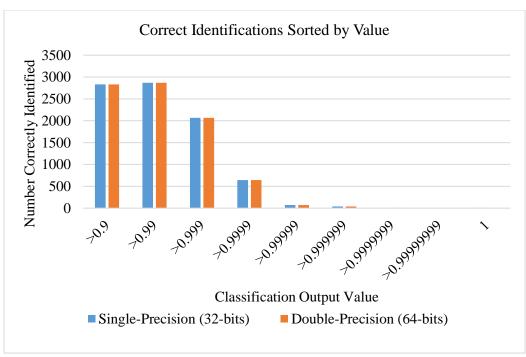

From this data, we can see that for both single and double precision data types there are 8,524 out of 10,000 images correctly identified with a 'strength' of 0.9 or above. This data was examined further to find any differences between results with these data types. The graph below looks at the 8,524 correctly identified results, then breaks this data down further into different ranges.

Figure 3.5

Further comparison of the 'strength' greater than 0.9 of single and double precision data-types.

|                       | >0. | >0.9 | >0.99 | >0.999 | >0.9999 | >0.99999 | >0.999999 | >0.999999 |   |

|-----------------------|-----|------|-------|--------|---------|----------|-----------|-----------|---|

|                       | 9   | 9    | 9     | 9      | 9       | 9        | 9         | 99        | 1 |

| Single-Precision (32- | 283 |      |       |        |         |          |           |           |   |

| bits)                 | 2   | 2867 | 2067  | 644    | 71      | 38       | 0         | 0         | 5 |

| Double-Precision (64- | 283 |      |       |        |         |          |           |           |   |

| bits)                 | 2   | 2867 | 2067  | 643    | 72      | 38       | 4         | 1         | 0 |

Table 3.7

Corresponding data used for comparison of 'strength' greater than 0.9 of single and double precision datatypes.

The data in the above table and graph can be broken down such that the first column represents which of the values are >0.9 and <=0.99, the second column represents values >0.99 and <=0.999, and on. Then the second to last column is values >0.999999999 and <1, and finally the last column represents values that are equal to 1. From this data, you can see the main difference is that when using single-precision data types, there are 5 results that have a value of 1.0, meanwhile when using double precision, there are no results that have a value of 1.0. I will go into more detail interpreting these results in the next section.

# 3.3 Accuracy Comparison

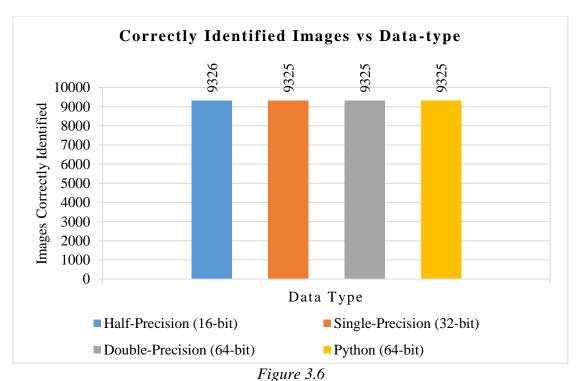

The accuracy of the Matlab implementation of the neural network can be compared with the Python results obtained when training the network. This is because the network has the same weights and biases, and we are using the same 10,000 MNIST test images in order to test the network. The comparison of results is shown below.

Comparison of digit recognition accuracy of Matlab implementations with Python results.

In Python, the weights and biases are created using 64-bit floating point numbers, therefore all the weights and biases are 64-bit, and must be converted to 32-bit and 16-bit for single and half precision. From this data we can see that the Python results, single, and double precision results are all the same. Surprisingly, the half-precision results in Matlab correctly identified 9326 values out of the 10,000. This is one better than all other

results and is unexpected. Another set of weights and biases for the network was created in Python, this time correctly identifying 9267/10000 images. These weights and biases were then run in Matlab, where all half, single, and double precision implementations correctly identified 9267/10000 images. Therefore the discrepancy seen in the results above is most likely associated with a slight change in internal numbers when changing to lower granularity at half-precision.

This difference can be attributed to the fact that doubles are more precise than singles, just as the name would suggest. For single precision numbers, any values with precision of 0.99999998 or greater are not able to be represented. These numbers are then converted to 1.0 when represented in single-precision floating point. For double-precision numbers meanwhile, these numbers are able to be represented. This is why the for double precision values, there are 5 numbers that are >0.9999999 and <1.0, and for single precision there are no values and 5 that are equal to 1.0.

Overall, the results have proven the proposed network design for half, single, and double precision data types. Comparing all of these results with the initial Python results, we can see that there is no discernible difference when using different precision data types. Once I had these results I could start the process of taking this design and implementing it in hardware.

#### CHAPTER 4:

### HARDWARE IMPLEMENTATION

## 4.1 Hardware Design Architecture

When thinking about implementation in hardware, the first thing was to break the algorithm down by the operations that would need to happen. We can take equation for the output of the hidden layer neurons in section 3.1, and write it as the following:

$$output(x) = \frac{1}{1 + \exp(-K - b_x)}$$

where  $K = \sum_{i=1}^{784} wx_i * p_i$

This allows us to break the problem of finding the output of a hidden layer neuron down into two parts. First, we need to multiply all 784 input pixels by their corresponding weights, then sum those values into one result. Second, we need to take that summed value and plug it into the sigmoid function. This involves five different operations; first taking the negative value of the summed result, then subtracting bias, then taking exp to that value, then adding a value of 1, then finally taking the reciprocal.

A visual representation of the multipliers and adders going into the first layer hidden neurons.

In this representation we are assuming that each operation has a latency of one clock cycle. We can see that in the first clock cycle, we are using 784 multipliers to multiply the input pixels by their correct weights. There are then 10 stages of cascading adders to sum the results up into one final value. This value is then used as the input for the second part in finding the output of the hidden layer neurons. This stage is shown below.

| Clock Cycle:     | 12       | 13       | 14  | 15      | 16    | 17                  |

|------------------|----------|----------|-----|---------|-------|---------------------|

|                  | Negative | sub bias | exp | add 1.0 | Recip |                     |

| Adder10_1_result | Negative | Sub blas | СХР | add 1.0 | Кесір | Neuron_final_result |

Figure 4.2

A visual representation of the results from the multipliers and adders going into the final operations of the neuron.

In the above image, we can see the second stage where we are taking the negative value of our result, subtracting the bias, taking that answer to exp, adding 1, then finally taking the reciprocal. This whole process takes another 5 clock cycles, if we assume a latency of one cycle for every operation. Putting the two steps together, it takes a total of 16 clock cycles in order to find the output of a the hidden layer neuron.

The second stage in the hardware involves taking the outputs of the hidden-layer neurons, then plugging those values into the following equation:

$$final\_output(x) = \frac{1}{1 + \exp(-K - b_x)}$$

Where

$$K = \sum_{i=1}^{12} wx_i * hidden\_output_i$$

This stage is implemented in a similar manner as the first stage, but instead of 784 inputs, we only have 12 this time. A visual representation is shown below.

| Clock Cycle: | 1                     | 2        | 3        | 4           | 5        | 6        | 7        | 8   | 9       | 10    | 11                  |

|--------------|-----------------------|----------|----------|-------------|----------|----------|----------|-----|---------|-------|---------------------|

|              | 1                     |          | 3        | 4           | 3        | U        | /        | 0   | 9       | 10    | 11                  |

| Hidden_out1  | Multiplier1           |          |          |             |          |          |          |     |         |       |                     |

| Weight_x_1   |                       | Adder1 1 |          |             |          |          |          |     |         |       |                     |

| Hidden_out2  | NAI±!I!               | AddCi1_1 |          |             |          |          |          |     |         |       |                     |

| Weight_x_2   | Multiplier2           |          | Adder2 1 |             |          |          |          |     |         |       |                     |

| Hidden_out3  | NAltimlian2           |          | Adderz_1 |             |          |          |          |     |         |       |                     |

| Weights_x_3  | Multiplier3           | Adder1 2 |          | Adder3 1    |          |          |          |     |         |       |                     |

| Hidden_out4  | NAlaindinu4           | AddCi1_2 |          | Adders_1    |          |          |          |     |         |       |                     |

| Weights_x_4  | Multiplier4           |          |          |             |          |          |          |     |         |       |                     |

|              | •••                   |          |          |             | Adder4 1 | Negative | sub bias | exp | add 1.0 | Recip |                     |

|              | •••                   | •••      |          |             |          |          |          |     |         |       | Neuron_final_result |

| Hidden_out9  | Multiplier9           |          |          |             |          |          |          |     |         |       |                     |

| Weight_x_9   | Multipliers           | A-1-11 F |          | Danistana a |          |          |          |     |         |       |                     |

| Hidden_out10 | Multiplier10          | Adder1_5 |          | Register2_3 |          |          |          |     |         |       |                     |

| Weight_x_10  | Multiplier10          |          | Adder2 3 |             |          |          |          |     |         |       |                     |

| Hidden_out11 | Name in the second of |          | Adderz_5 |             |          |          |          |     |         |       |                     |

| Weights_x_11 | Multiplier11          | Adder1 6 |          |             |          |          |          |     |         |       |                     |

| Hidden_out12 | Multiplier12          | Adder1_6 |          |             |          |          |          |     |         |       |                     |

| Weights_x_12 | iviuitipiier12        |          |          |             |          |          |          |     |         |       |                     |

Figure 4.3 A visual representation of the operations of a single output layer neuron.

In this stage, because there are only the 12 inputs, it takes only takes 4 layers of adders to sum the multiplication results, this allows the entire process of calculating the result of the final layer neurons to take only 10 clock cycles.

The design described above describes the components needed for one neuron in the hidden layer, and one neuron in the output layer. This design can be implemented for every neuron in the hidden layer, as well as every neuron in the output layer by repeating the design 12 and 10 times respectively. You can also pipeline the design by in the first clock cycle use the data for the first hidden layer neuron, on second clock cycle use data for second layer neuron, etc. This adds complexity because to begin calculations for the output layer neurons, you must first know the results from all the hidden layer neurons. I have compared the latency and resource usage for these two approaches below.

|           | Latency<br>(clock cycles) | Multipliers | Adders | Subtractors | Exponential | Reciprocal |

|-----------|---------------------------|-------------|--------|-------------|-------------|------------|

| Non-      |                           |             |        |             |             |            |

| pipelined | 26                        | 9528        | 9528   | 44          | 22          | 22         |

| Pipelined | 48                        | 796         | 796    | 4           | 2           | 2          |

Table 4.1

A comparison of the resources needed for a pipelined vs non-pipelined design.

When comparing these two approaches, you can see that even though the non-pipelined approach is nearly twice the speed of the pipelined approach, it uses nearly 12 times the resources. Because of this issue, I decided to go with a design that would be pipelined, in order to lower my resources usage. I still had issue with the fact that the number of multipliers and adders was so high.

With this problem in mind, I decided to break down the multiplication of the first layer weights and inputs into 8 different steps. This portion of the design accounts for 784/796 multipliers and 783/796 adders, if I break this down into multiple parts, I can lower the overall resource utilization tremendously.

This design keeps the same pipelined structure for the output level neurons, but for the hidden layer neurons, instead of 784 multipliers followed by adders, we will only have 98. This design is shown below.

|              |                | _         |            |           | _        | _        | _        |          |

|--------------|----------------|-----------|------------|-----------|----------|----------|----------|----------|

| Clock Cycle: | 1              | 2         | 3          | 4         | 5        | 6        | 7        | 8        |

| Pixel1       | Multiplier1    |           |            |           |          |          |          |          |

| Weight_x_1   | Multiplier     | Addorf 1  |            |           |          |          |          |          |

| Pixel2       | Multiplier2    | Adder1_1  |            |           |          |          |          |          |

| Weight_x_2   | Multiplier2    |           | Addor 1    |           |          |          |          |          |

| Pixel3       | Multiplier3    |           | Adder2_1   | Addor2 1  |          |          |          |          |

| Weights_x_3  | Multipliers    | Adder1 2  |            | Adder3_1  | Adder4 1 |          |          |          |

| Pixel4       | Multiplior4    | Addel1_2  |            |           | Adder4_1 | AddorE 1 |          |          |

| Weights_x_4  | Multiplier4    |           |            |           |          | Adder5_1 | Adder6 1 |          |

|              |                |           |            |           |          |          | Addcro_1 |          |

|              |                |           |            |           |          |          |          | Adder7_1 |

| •••          |                | •••       | •••        | •••       | •••      | •••      |          | _        |

| Discolor     |                |           |            |           |          |          | Adder6_2 |          |

| Pixel95      | Multiplier95   |           |            |           |          | Adder5 3 |          |          |

| Weight_x_95  |                | Adder1 48 |            |           | Adder4 6 |          |          |          |

| Pixel96      | Multiplier96   | AddCl1_40 |            | Addor2 12 | Addc14_0 |          |          |          |

| Weight_x_96  | Multiplier90   |           | Adder2 24  | Adder3_12 |          |          |          |          |

| Pixel97      | Multiplier97   |           | Addel Z_Z4 |           |          |          |          |          |

| Weights_x_97 | Widitiplier97  | Adder1 49 |            |           |          |          |          |          |

| Pixel98      | Multiplier98   | Addel1_49 |            |           |          |          |          |          |

| Weights_x_98 | With third 198 |           |            |           |          |          |          |          |

Figure 4.4 A visual representation of the first stage multiplication with 98 multipliers.

With this design, we are able to process 98 inputs with each iteration. So we will have to have 8 iterations in order to process all the inputs for a neuron. The way the design works is like a pipeline within a pipeline. For the first input neuron, we have to run the above 98 multiplier adder sequence 8 times. As the results from each eighth of the multiplications come through they are added together in an accumulator. An idea of how the accumulator fits into the output of the hidden layer neurons is shown below.

| Clock Cycle:    | 9      | 10     | 11     | 12     | 13     | 14     | 15     | 16     | 17       | 18       | 19  | 20      | 21    | 22                  |

|-----------------|--------|--------|--------|--------|--------|--------|--------|--------|----------|----------|-----|---------|-------|---------------------|

| Adder7 1 result | Accum1 | Accum2 | Accum3 | Accum4 | Accum5 | Accum6 | Accum7 | Accum8 | Negative | sub bias | ехр | add 1.0 | Recip | Neuron final result |

Figure 4.5

A visual representation of the accumulation and final operations used after the 98 multipliers.

Looking at the above image, you can see at cycle 9 the first value from the multiplier-adder comes in. For 8 cycles these values are accumulated to get one final value for all 784 inputs. Once this value has been found, the result is just sent into the same sequence, of taking the negative, subtracting bias, taking exponential, adding 1.0, then taking the reciprocal. This entire process ends up taking 21 cycles to find the result. A comparison of the resource utilization and latency of this design compared to pipelined and non-pipelined is shown below.

|               | Latency (clock cycles) | Multipliers | Adders | Subtractors | Exponential | Reciprocal |

|---------------|------------------------|-------------|--------|-------------|-------------|------------|

| Non-pipelined | 26                     | 9528        | 9528   | 44          | 22          | 22         |

| Pipelined     | 48                     | 796         | 796    | 4           | 2           | 2          |

| Pipelined/98- |                        |             |        |             |             |            |

| mul           | 129                    | 110         | 110    | 4           | 2           | 2          |

*Table 4.2*

A comparison of the resources needed for a pipelined, non-pipelined design, and pipelined with 98 multipliers designs.

We can see that by adding this change, we are using 13.8% the number of multipliers and adders as the fully-pipelined design and 1.15% the number of multipliers and adders as the non-pipelined design. This does come at a cost of a higher latency, but given that the overall number of cycles needed for the network to classify one image is only 129, this still remains very low and still feasible for real-time applications. Because of these results, the hardware design architecture was finalized as the fully-pipelined design with 98 multipliers for the first hidden-layer.

### 4.2 Final Hardware Architecture

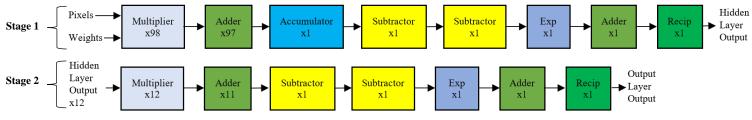

The design and tradeoffs of the various non-pipelined, pipelined, and pipelined with 98 multiplier architectures were discussed at length in the previous section. In this section I will describe the components used in the final architecture, and how they are connected.

Figure 4.6

A visual representation of all the components of the design put together.

The above diagram shoes the connection of the hardware components. Stage 1 is used for finding the output of the hidden layer neurons, and stage 2 is used for finding the output of the output layer neurons. In stage 1, the 98 multipliers and 97 cascading adders are used 8 times, feeding the result each time into the accumulator. This allows the network to process all 784 input pixels and their corresponding weights. Once the accumulator has accumulated all 8 summed values, the results propagate sequentially

through the rest of stage 1. Stage 1 is pipelined for all 12 of the hidden-layer neurons.

Once all 12 of the stage 1 outputs have been calculated, stage 2 processes the results of the output layer neurons sequentially. Stage 2 is again pipelined for all 10 output neurons.

# 4.3 Timing and RTL Design

#### 4.3.1 How the Counters are Used

Given the pipelined nature of the design, timing became very important in making sure that at any given moment the input pixels, weights, and biases were correct. The way that this problem was solved was by using six different counters that would serve as references for different inputs and outputs within the design.

- <u>Counter 1</u>: Used to control the input pixels and weights that are being input into the 98 multipliers of stage 1.

- Counts from 0-9. Increments counters every clock cycle. Resets to 0 when it reaches a value of 9.

- o Enabled when the entire network is enabled.

- Inputs/weights change from 0-7, then two extra cycles allow for accumulator to be reset in between neurons.

- <u>Counter 2</u>: Used to control for which neuron the input weights in stage 1 will correspond to.

- Counts from 0-11. Increments every time Counter 1 reaches 9 and resets to 0. Resets to 0 when it reaches a value of 11 and Counter 1 reaches value of 9.

- Enabled when the entire network is enabled.

- Changes the input neuron weights every time it is incremented, cover all hidden layer neurons (0-11).

- Counter 3: Used to control the when accumulator is used.

- Counts from 0-9. Increments every clock cycle. Resets to 0 when it reaches a value of 9.

- $\circ$  Enabled when Counter 1 = 8 and Counter 2 = 0.

- Used to enable to accumulator when Counter 3 is enabled and less than 8,

and to resets the accumulator when Counter 3 is greater than 7.

- Counter 4: Used to control when the output of the hidden layer neuron is valid.

- Counts from 0-9. Increments every clock cycle. Resets to 0 when it reaches a value of 9.

- $\circ$  Enabled when Counter 1 = 6 and Counter 2 = 1.

- When Counter 4 = 5, the result is stored to a location in a buffer,

dependent on the value of Counter 5.

- <u>Counter 5</u>: Used to tell to which neuron (0-11) a valid hidden layer neuron result is stored.

- Counts from 0-11. Increments every time Counter 4 reaches 9 and resets

to 0. Resets to 0 when it reaches a value of 11 and Counter 4 = 9.

- Enabled when entire network is enabled.

- Tells which valid result corresponds to which neuron (0-11) in the hidden layer results buffer.

- Counter 6: Used to tell when the output of the output layer neuron is valid.

- Counts from 0-19. Increments every clock cycle. Resets to 0 when it reaches a value of 19.

- Enabled when Counter 4 = 9 and Counter 5 = 11.

- Signals when the output of the entire network is valid. When Counter 6 =

0xa, the result corresponds to output-neuron[0] value, Counter 6 = 0xb

corresponds to output-neuron[1] value, ..., Counter 6 = 0x13 corresponds to output-neuron[9] value.

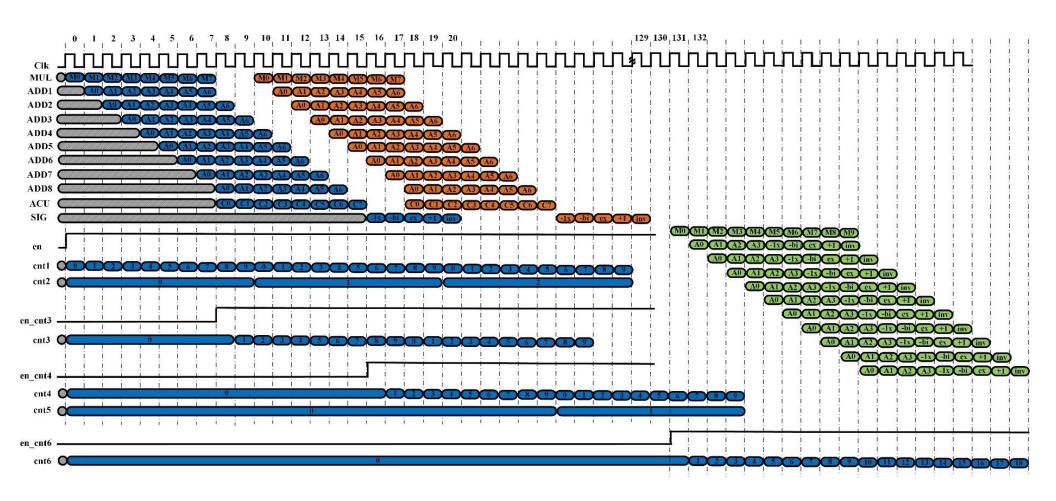

A diagram showing all timers in line with tasks of the network is shown in figure 4.7 on the next page.

Figure 4.7 A visual diagram of the timing of operations aligned with counters.

In the above diagram, you can see the sequential nature of how the result from M0 feeds into ADD1, which then takes 7 clock cycles to add the 98 results together, then at clock cycle 8, the accumulator starts adding together the 8 results, then feeding them into the sigmoid operations. Underneath these operations, you can see how the counters line up and signal correctly for all the attributes listed above.

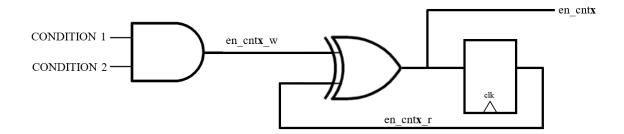

## 4.3.2 RTL Design