# An Approach of Project-Based Learning: Bridging the Gap Between Academia and Industry Needs in Teaching Integrated Circuit Design Course

Xiaokun Yang<sup>10</sup>, *Member*, *IEEE*

Abstract—In teaching an integrated circuit (IC) design course, 2 many benefits can be gained by offering an industry-relevant <sup>3</sup> project associated with a training to a bundle of electronic design 4 automation (EDA) tools and design methodologies. However, few 5 open-source projects were able to cover the key qualifications 6 needed by industry. Therefore, this article proposes an approach 7 of project-based learning (PBL), aiming at bridging the gap 8 between the industry needs and the learning outcomes from 9 academia. Specifically, this article first conducts an investigation 10 on basic qualifications necessary for entry-level IC designers. By 11 summarizing those results as a specification, the development, 12 implementation, and assessment to an open source project is 13 presented to include the latest EDA tools and methodologies 14 needed by IC design companies, as well as the fundamental 15 knowledge and skills of the course outcomes. The effectiveness 16 of this work is evaluated by the analysis of students' final exam 17 results using t-tests. It shows that students who had participated 18 in the project achieved higher levels of acquired knowledge to the <sup>19</sup> design on ICs. Student survey and evaluation also demonstrate 20 positive effect on student achievement with the PBL approach. 21 Further, the public availability of this project has a big potential 22 to offer a framework to practical courses and improve stu-23 dents' knowledge and skills in many topics, such as computer 24 architecture and micro-systems.

Index Terms—Industry-relevant project, integrated circuit

(IC), project-based learning (PBL), system-on-chip (SoC).

#### 27

# I. INTRODUCTION

PROJECT-BASED learning (PBL) is a significant requirement in teaching engineering courses, providing opportunities to learn and apply knowledge and skills tied to college and career readiness [1], [2]. Many practical projects and methodologies thus have been developed to allow students to tackle real-world challenges and encourage criticalthinking [4], [11]. And some of the projects were directly from industry [5]. However, few PBL focused on exploring the key qualifications needed by chip design companies, resulting in a gap between knowledge and skills gained in universities and the real practical experiences needed by industry.

On the industry side, the interaction between academia and electronic design automation (EDA) tool vendors has proven to be successful in the field of integrated circuit (IC) design.

The author was with the Silicon 3D Engineering, Beijing Research and Development Center, Advanced Micro Devices Inc., Beijing 100190, China. He is now with the Department of Engineering, University of Houston-Clear Lake, Houston, TX 77059 USA (e-mail: yangxia@uhcl.edu).

Digital Object Identifier 10.1109/TE.2021.3050450

Traditionally, companies provide special topics lectures for 42 universities to keep them aware of new aspects and targets 43 in industry. For example, Synopsys provides universities with 44 access to comprehensive curricula for Bachelor and Master 45 Programs in IC design and EDA development [6]. Another two leading EDA vendors—Cadence and Mentor Graphics—offer 47 the similar University Programs called Cadence University 48 Software Program [7] and Higher Education Program for 49 Mentor Graphics [8]. However, all teaching resources from 50 such University Programs are available for members only. The 51 projects are mainly based on licensed EDA tools. 52

Another two leading field-programmable gate array (FPGA) 53 vendors-Altera (now Intel) and Xilinx-also provide a 54 friendly service to academics [9], [10]. For example, Xilinx 55 University Program (XUP) collaborates with academics to 56 develop and deliver many lab materials. To encourage instruc-57 tors and researchers use their tools and technologies, XUP 58 also provide workshop materials which are freely accessible to 59 academics to use in classes. The provided experiments are fun-60 damental logic designs, target at training students to use their 61 EAD tools, and FPGAs, which are not suitable for teaching 62 system-level designs on an IC, or system-on-chip (SoC).

On the university side, there are two main challenges to 64 provide PBL in line with industry requirements. First, it is dif-65 ficult for academics to obtain direct experience in designing an 66 application-specific IC (ASIC), particularly in the SoC level. 67 Instructors would be struggling with the complicated indus-68 trial design flow involving register-transfer level (RTL) design 69 rules and coding style, automatic verification/simulation envi-70 ronment, synthesis results of behavioral models, timing issues, 71 design constraints, and so on. Second, due to the time limi-72 tation of a semester-long course, it is often not feasible to 73 expect students to finish a project through the entire FPGA 74 design flow involving a bundle of tools and methodologies. 75

To overcome the aforementioned challenges, this article proposes the development, implementation, and assessment with an open source project in teaching an IC design course. As a design-focused curriculum, the system-level verification environment can be shared to students to rapidly validate and demonstrate the SoC design. Specifically, the main contributions of the proposed work are below.

Conducts an investigation to the key qualifications

needed for entry-level IC designers. By summarizing

those results as a specification, an approach of PBL

using an open source project is further proposed, enables

0018-9359 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information.

Manuscript received June 1, 2020; revised August 10, 2020 and November 30, 2020; accepted January 3, 2021.

- Presents the details of the implementation, including the

design schedule, pedagogical approaches, and the exper imental results in terms of simulation, area-speed-power

- estimation, and the final FPGA demonstration.

3) The assessment is based on an evaluation of the

final exam using *t*-tests, showing significantly better

performance for students had participated in the project.

The project is publicly available in order to serve more

practical courses related to the design on digital systems. The organization of this article is as follows. In Section II, the related works are discussed. Section III conducts the investigation on basic qualifications of industry needs. Seeing the investigation result as a specification, Sections IV and V roz introduce the proposed PBL containing the project, schedule, and pedagogical approaches. In Section VI, the experimental results are detailed and in Section VII, the student survey and evaluation are described. Finally, Section VIII presents the concluding remarks and Section VIII-A discusses the future work of this article.

#### 108

## II. RELATED WORKS

Prior researches to PBL have been dedicating to effectively narrow the gap between industry and the engineering educatin tion [15], [16]. As an example, Oguz and Oguz [15] compiled a list of skills that are sought by the software companies, comnspection of 50 advertisements for the software engineering position. Together with many collected information like interviews to students and recent graduates, it concluded that project experience is the best cure to narrow the gap.

A case study for using PBL combined with collaborative laborative (CL) and industry best practices was presented in [17]. Through building a modular management system in an embedded systems course, it showed an improvement of teaching, lal learning, and student assessment processes. To the specific IC design course, in [18], an analog IC design flow was introduced with a major project—an RFIC integrated by mixer, power amplifier, and low noise amplifier using 65-nm technology.

In contrast, the IC design in the digital world is a bit 125 126 different in terms of a bundle of EDA tools and FPGA demon-127 stration. Exiting research to the digital IC design courses ainly focused on either fundamental logic level [21], [22] or 128 m software-hardware co-design platforms which are most likely 129 130 for microcontroller programming and computer architecture courses [19], [20]. For instance, a flexible VHDL framework 131 <sup>132</sup> for simulation and synthesis was presented in [22], providing a 133 simple and intuitive method to implement basic logic circuits. <sup>134</sup> In [19], an FPGA-based education platform was presented to 135 support the experiments from hardware systems to vision algo-136 rithms. It was equipped with the Xilinx PYNQ-Z2 board where CPU host and an FPGA in the same chip are integrated. The 137 a 138 flexibility to use the ARM processor can significantly reduce 139 the design complexity on hardware; nonetheless, the program-<sup>140</sup> ming experience on an ARM core is most likely the teaching outcomes of a microcontroller programming course. 141

Therefore, this article proposes an approach of PBL by tas carrying out a pure RTL design on FPGA. By researching and

TABLE I Key Qualifications of Industry Needs

| Requiremnets                 | Basic Qualifications                                                                                                         |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Design Flow                  | 1. ASIC and/or FPGA Design Flow                                                                                              |  |  |

|                              | 2.1 Verilog/VHDL                                                                                                             |  |  |

| HDL<br>Programming           | 2.2 Editor - VIM/Emacs/WinEdt                                                                                                |  |  |

|                              | 2.3 Linux OS                                                                                                                 |  |  |

|                              | 2.4 Scripts such as Perl, tcl, and Makefile                                                                                  |  |  |

| Simulation<br>(Verification) | 3.1 Development/implementation of test plans,<br>verification (simulation) environments, validation<br>components, and tests |  |  |

|                              | 3.2 Simulators - Synopsys VCS/Cadence NC/<br>Mentor Graphic ModelSim                                                         |  |  |

| FPGA Demo                    | 4.1 FPGA tool - Xilinx Vivado/Intel Quartus                                                                                  |  |  |

| TT GIT Denio                 | 4.2 FPGA prototype and debug                                                                                                 |  |  |

|                              | 5.1 Bus architecture such as AXI and Wishbone                                                                                |  |  |

| Design Related               | 5.2 SoC peripherals such as I2C, VGA, Timer                                                                                  |  |  |

|                              | 5.3 RTL IP, Vivado/Quartus IP, and design reuse                                                                              |  |  |

|                              | 5.4 Basic design rules such as FSM, clock domain crossing, and FIFO                                                          |  |  |

|                              | 5.5 Tradeoff between quality and design cost                                                                                 |  |  |

seeing the industry needs as a specification, the proposed PBL 144 learning is able to cover most key qualifications necessary by 145 industry. 146

#### III. RESEARCH ON BASIC QUALIFICATIONS

147

This section conducts an investigation to the specific <sup>148</sup> requirements for an entry-level chip designer, including the <sup>149</sup> FPGA Hardware Engineer from Mentor Graphics, Digital <sup>150</sup> IC Design (PHY) Engineer from Apple, Design Verification <sup>151</sup> Engineer from AMD, and many more. The research is based <sup>152</sup> on the information on Indeed.com and Linkedin.com by filtering the relevance of full-time job type and entry-level <sup>154</sup> experience. After compiling the details of 20 posted job <sup>155</sup> opportunities, the key qualifications needed by industry are summarized in Table I. <sup>157</sup>

The ASIC/FPGA design flow is necessary as shown in the second row of this Table (or item 1). Apart from the hardware description language (HDL) (item 2.1) and one of the editor software (item 2.2), the basic Linux command (item 2.3) and one of the script languages (item 2.4) are needed because the chip design environment is usually Linux/Unix based and multiple scripts involved.

In the front-end, simulation experience, including development of test plans, simulation environment, bus function models (BFMs), scoreboards/monitors, and test cases, is required (item 3.1). In order to run simulation in RTL or netlist level, 168 one of the simulators is a must (item 3.2). The dominant simulators in industry include Mentor Graphics ModelSim/Questa, 170 Synopsys VCS, and Cadence NC. Additionally, FPGA demonstration is needed where students can rapidly exercise and 172 validate their design of interest (item 4.2). The FPGA tools 173 include Intel Quartus and Xilinx Vivado (item 4.1). 174

To bring real-life context and technology to the curriculum, <sup>175</sup> it is imperative to devise a project with industry standards and <sup>176</sup>

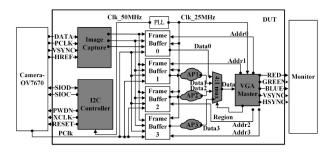

Fig. 1. Design architecture.

<sup>177</sup> protocols. As an entry-level position, first, the project expe-<sup>178</sup> rience should cover basic design methods and design rules, <sup>179</sup> such as the clock domain crossing (CDC), finite-state machine <sup>180</sup> (FSM), synchronous/asynchronous FIFOs (item 5.4), and the <sup>181</sup> design constrains in terms of area-speed-power (item 5.5). <sup>182</sup> Further, some widely used industrial protocols like bus archi-<sup>183</sup> tectures (item 5.1) and bus peripherals, such as I2C and UART, <sup>184</sup> should be studied (item 5.2). The submodule implementa-<sup>185</sup> tion is usually named intellectual property (IP) level design, <sup>186</sup> compared with system-level integration. All the IPs, including <sup>187</sup> third-party designs and self-designs, would be integrated into <sup>188</sup> an SoC (item 5.3).

#### 189 IV. OVERVIEW OF THE OPEN SOURCE PLATFORM

As per the investigation mentioned above, this section presents an approach of PBL aiming to cover all the items listed in Table I. The experiments have run for three semesters, with 10 graduate students in Spring 2017, 12 in Fall 2017, and 13 in Spring 2019. One instructor and one teaching assistant (TA) worked to provide tutorials and training, and helped in the HDL programming and performance evaluation. The details of the project and schedule are introduced in this section.

## 198 A. Project Description

Generally, the project is based on an open-source platform 199 published in [12], capable of capturing images by interfacing 200 an OV7670 camera and displaying both the original images 201 and the results of grayscale images on a VGA-interfaced 202 monitor. The design architecture is shown in Fig. 1, mainly 203 204 containing three interfaces: 1) an I2C master; 2) a VGA mas-205 ter; and 3) an Image Capture slave. The I2C master is used to set up the OV7670 camera. After being configured, the cam-206  $_{207}$  era enables to send  $320 \times 240$  size of images into the Frame <sup>208</sup> Buffer #0 via the Image Capture interface.

To study the design tradeoff between quality of results and resource cost on FPGA, in Fig. 1, three approximate designs—AP1, AP2, and AP3, on color-to-grayscale converter are integrated into the SoC. In theory, the higher the approximation levels, the more hardware resource can be saved. To high the minimum design cost corresponding to the quality bound is the basic idea of IC design. Further, Frame Buffers 1, 2, and 3 are used to store the results from approximate design 1, 2, and 3, respectively. And then the VGA master reads data out from the four Frame Buffers and display the data pixel by pixel on a 640 × 480 size of monitor.

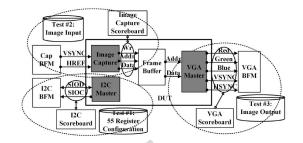

Fig. 2. Verification (simulation) environment.

TABLE II Project Schedule

| Course                        | Торіс                                                                                        | WKs  | HRs |

|-------------------------------|----------------------------------------------------------------------------------------------|------|-----|

| Lectures                      | Introduction on IC design flow, Verilog<br>HDL, Design rules and constraints, etc.)          | 1-5  | 15  |

| Laboratory<br>(Mini Project)  | Training: VIM, ModelSim, and Vivado;<br>simulation env, Nexys 4 FPGA                         | 6-7  | 6   |

| Lecture                       | Industry specifications:<br>AMBA AXI, I2C, VGA, and OV7670                                   | 8    | 3   |

| Laboratory<br>(Final Project) | IP design and verification;<br>SoC integration and verification;<br>FPGA demo and evaluation | 9-13 | 15  |

| Laboratory<br>(Final Project) | Discussion and presentation, project assessments                                             | 14   | 3   |

The verification/simulation environment is shown in Fig. 2, 220 including design-under-test (DUT), bus function models 221 (BFMs), scoreboards, and test vectors. Specifically, each 222 design interface is equipped with a bus function model for 223 driving/responding the interface and a scoreboard for testing 224 the functionalities. The environment is controllable by a tcl 225 script to compare data between design interfaces and golden 226 models. 227

## B. Project Schedule

In addition to the midterm week, each full-semester course <sup>229</sup> contains 14 weeks, including lectures and projects. The curriculum schedule of the Spring 2019 semester is shown in <sup>231</sup> Table II. Six weeks—from the first week to the fifth week, <sup>232</sup> plus the eighth week—are spent to introduce all the theories <sup>233</sup> and principles. In the eighth week, specifically, the industry <sup>234</sup> standards, including I2C, VGA, and OV7670 data sheet, are <sup>235</sup> explained by the instructor. The interfaces and timing diagrams of theses standards are the design specification of the <sup>237</sup> final project. The rest of eight weeks focus on conducting the <sup>238</sup> final project. All the programming language, EDA tools, and <sup>240</sup> applied by carrying out the project for a thorough and practical <sup>241</sup> understanding of theoretical concepts.

# V. PEDAGOGICAL APPROACHES AND PROJECT 243 IMPLEMENTATIONS 244

In this section, the pedagogical approaches related to the 245 PBL is discussed. Then, the details of the project implemen- 246 tation is further introduced. 247

228

#### 248 A. Pedagogical Approaches

The final project can be divided into three phases: 1) the 249 <sup>250</sup> design phase; 2) implementation phase; and 3) testing phase. The design phase emphasizes learning industrial standards and 251 creating the design specification; the implementation phase 252 focuses on describing hardware and integrating SoC by Verilog 253 HDL; and the testing phase concentrates on the functional 254 verification and FPGA demonstration. 255

The main challenge of the design phase is lack of experience 256 create the SoC architecture with multiple industry specifi-257 to 258 cations. In this phase, the instructor gives an overview to the system architecture, as well as explains the block and timing 259 260 diagrams to each submodule. Much interactive discussion of the main concepts should be involved in this phase. 261

In the implementation phase, the big challenge for stu-262 <sup>263</sup> dents is to think in hardware when programming with Verilog <sup>264</sup> HDL. Not only the industry design rules but also good coding 265 style should be emphasized by the instructor. Additionally, 266 two training classes are offered to help students utilize the 267 EDA tools, build a typical test bench, and demonstrate basic <sup>268</sup> combinational and sequential circuits on FPGA.

The testing phase consists of simulation on IPs and SoC, as 269 270 well as FPGA demonstration. The simulation has always been <sup>271</sup> neglected to teach such courses, which is actually crucial to the 272 front-end development of IC design flow. IP-level test bench and the final FPGA demonstration should be completed by 273 students with instructor and TA's support. However, to build 274 system-level verification environment is not feasible to a 275 a semester-long and design-focused course. Therefore, the open-276 277 source test bench will be explained by the instructor and then 278 provided to students to rapidly verify their SoC integration.

#### Project Implementations With Learning Method 279 B.

The main contribution of this article is to present a PBL 280 <sub>281</sub> approach to cover items of basic qualifications in Table I. 282 Hence, this section discusses the details of the project implementation in Table III to check all the items one by one. 283

In the sixth and seventh weeks, a mini project-design on a 284 285 timer—is given to students to take practice for FPGA demonstration and using the EAD tools, including VIM, Mentor 286 Graphic ModelSim, and Xilinx Vivado. Through the two-287 eek training, students learn how to build a simple simulation 288 289 environment and run the FPGA design flow. The instruc-290 tor coordinates and supports students' work by offering the training tutorials and relevant references of the EDA tools. 291

Starting at the ninth week, the instructor helps students 292 293 create the block diagram of the SoC architecture contain-<sup>294</sup> ing three submodules or IPs—the I2C master, Image Capture 295 slave, and the VGA master. In what follows, students are split <sup>296</sup> into three teams, four to five students per group. Each group 297 completes design and simulation of one submodule (item 5.2 <sup>298</sup> covered as shown in the second column). Students should finish the submodule design specification in the ninth week. And 299 300 in the tenth week, students focus on the HDL programming and simulation (items 2.1-2.4, 3.1-3.2, 5.4 covered). During 302 the submodule implementation, the teams continuously report 303 and present their progress and results to the instructor who

TABLE III PROJECT IMPLEMENTATION AND KNOWLEDGE AND SKILLS GAINED FOR THE THREE GROUPS

| Group                              | WKs &<br>Items              | Tasks                                                                                          | Knowledge and Skills                                                                                                                           |

|------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2,<br>3                         | 6-7                         | Mini Project:<br>Design and verify<br>the functionality<br>of a Timer                          | Basic design with Verilog,<br>Use of VIM, ModelSim,<br>Vivado, and Nexys 4 FPGA                                                                |

| 1                                  | 9-10<br>(items<br>2.1-2.4   | Final Project (IP):<br>Design and verify<br>the functionality<br>of the I2C master             | Studying the I2C spec,<br>basic combinational and<br>sequential circuits design<br>including FSM, counter,<br>tri-state buffer, MUX, etc.      |

| 2                                  | 3.1-3.2<br>5.2, 5.4)        | Final Project (IP):<br>Design and verify<br>the functionality<br>of the Image<br>Capture slave | Studying the Image<br>Capture spec,<br>basic combinational and<br>sequential circuits design<br>including concatenation,<br>dff, counter, etc. |

| 3                                  |                             | Final Project (IP):<br>Design and verify<br>the functionality<br>of the VGA master             | Studying the VGA spec,<br>basic combinationa and<br>sequential circuits design<br>including FSM, counter,<br>comparator, etc.                  |

| 1, 2, 11-12<br>(items<br>5.1, 5.3) |                             | Final Project (SoC):<br>SoC Integration                                                        | System-level design,<br>integration, and verification                                                                                          |

| 1, 2,<br>3                         | 13-14<br>(items<br>4.1-4.2) | Final Project (FPGA)<br>FPGA prototype                                                         | Synthesis, placement<br>& routing, and FPGA<br>demonstration                                                                                   |

provides coordination and help. Within the team, the students' 304 teamwork improves as the project progresses. 305

In the 11th week, each team shares their submodule design 306 to others, then integrates all the three IPs into an SoC 307 (items 5.1 and 5.3 covered). The system-level integration and 308 verification are performed in two weeks. The system test 309 bench is given to students to verify the SoC interfacing and 310 functionality. In the following 13th week, the synthesis and 311 placement and route are implemented to obtain the final FPGA 312 netlist (items 4.1 and 4.2 covered). Meantime, the system 313 performance can be evaluated in terms of slice count, latency, 314 and power consumption (item 5.5 covered). Finally, the whole 315 project implementation, activities, and the results should be 316 presented and discussed at the end of the semester. 317

#### VI. RESULTS OF SIMULATION, FPGA DEMONSTRATION, 318 AND DESIGN PERFORMANCE 319

In this section, the design simulation and FPGA demonstra- 320 tion are discussed. The results in real-life hardware schematic 321 and resource cost can inspire and encourage students to think 322 in hardware when coding Verilog HDL. 323

# A. Verification/Simulation

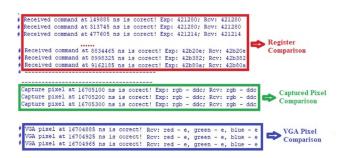

Students test the functionality of their designs in two steps— 325 simulation and FPGA demonstration. The IP-level simulation 326 should be mainly completed by students by group. After that, 327 instructor and TA involve in the system-level verification to the 328 SoC integration. Fig. 3 shows the simulation results by using 329 ModelSim. Through monitoring commands sent by the I2C 330

324

Fig. 3. Simulation results.

TABLE IV SOC RESOURCE COST ON FPGA

| Resource Cost | LUTs | Regs | RAM | IOs | TP (mW) |

|---------------|------|------|-----|-----|---------|

| SoC           | 774  | 297  | 106 | 34  | 220     |

master, the I2C interface design can be verified shown in the first box. In the second box, the design on the Image Capture slave is verified by comparing the data being stored into frame buffers and the data from golden files. As an example, the first pixel being checked is hexadecimal "ddc", including 4-bit red pixel (hexadecimal "d"), 4-bit green (hexadecimal "d"), and the design on the VGA master can be verified.

#### 339 B. Area-Speed-Power Evaluation

In what follows, the HDL design is synthesized into gatelevel netlist using Xilinx Vivado. Then the design performance in terms of slice count and power consumption is evaluated in Table IV. As depicted, the SoC design spends 774 slice LUTs, 297 slice registers, 106 block RAMS, and 34 IOs. Additionally, the total power (TP) consumption is 220 mW, ate including 102-mW static power and 118-mW dynamic power. During the back-end operation, students can learn how to estimate the chip size and power cost on FPGA. More important, it can help students match the behavioral model level design with the real hardware component, which is one of the biggest challenges for the beginners learning HDL.

# 352 C. Design Constrains

To find the optimal design corresponding to different quality bound is an important skill for IC designers. The knowledge, skills, and experience of industry design rules and coding style are thus crucial to students to describe a hardware system. As a case study, therefore three approximations of design on colorto-grayscale image converter are given to students to test the quality-resource tradeoff [13]. Table V shows the synthesis results of the exact design (EX) and approximate design 1, 2, and 3 (AP1, AP2, and AP3). It can be observed that the higher approximation of the design achieves higher maximum operational frequency (MOF) and more resource saving in terms of slice count and power dissipation.

TABLE V

Resource Cost on Color-to-Grayscale Converter

| Designs | LUTs | Regs | MOF (MHz) | Power (mW) |

|---------|------|------|-----------|------------|

| EX      | 264  | 382  | 230.264   | 21         |

| AP1     | 228  | 342  | 292.466   | 17         |

| AP2     | 106  | 172  | 353.788   | 15         |

| AP3     | 22   | 23   | 899.402   | 5          |

#### D. FPGA Demonstration

365

384

Finally, the SoC design and integration are demonstrated <sup>366</sup> and presented in the last laboratory session of the semester, <sup>367</sup> with a documentation report, including project design, implementation, and experimental results. <sup>369</sup>

| VII. | ASSESSMENT | 37 |

|------|------------|----|

|      |            |    |

The theoretical and practical knowledge and skills gained <sup>371</sup> via PBL learning are mainly estimated using the exam results. <sup>372</sup> The exam was taken by 35 graduate students, 22 students in <sup>373</sup> Spring 2017 and Fall 2017, and 13 students in Spring 2019. <sup>374</sup> The exam results are used to evaluate the following hypothe-<sup>375</sup> sis: after completing the project, students have increased their <sup>376</sup> theoretical and practical knowledge on the key qualifications <sup>377</sup> of the industry needs. The exam results of students who did or did not participate in the project are statistically compared by <sup>379</sup> *t*-tests to test the hypothesis. Additionally, a student survey was taken in Spring 2019 to show the students' response. Finally, <sup>381</sup> the student evaluations over the three semester are analyzed <sup>382</sup> to depict the improvement of the course by using PBL. <sup>383</sup>

#### A. Exam on Knowledge and Skills

The final exam can be divided into two parts: the knowledge 385 and skills on the design of ICs. The first part is used to evaluate 386 the most important knowledge needed by an entry-level IC 387 designer, and the second part is created for testing the practical 388 skills by using the theory. The first part is 40% of the final 389 grade and the second part is 60%. 390

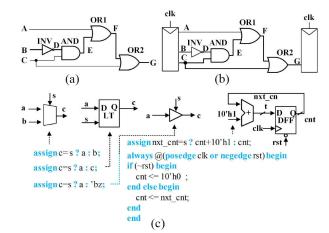

As one of the most important learning outcomes, the timing issue for designing digital circuits is tested in the first part. <sup>392</sup> Actually, the timing constraint is also one of the most common interview questions in industry, which somehow determines success or failure of the chip tape-out. For example, the true/false path and the setup/hold time constraint are tested in Fig. 4(a) and (b). Students should understand that the B-D-E-F-G path is the longest path in Fig. 4(a) but not the true path. Hence, the critical path for finding the MOF in Fig 4(b) should be the C-E-F-G path.

One of the biggest challenges for the beginners learning 401 HDL is to map the RTL design with a specific piece of 402 hardware. As an example in the second part, in Fig. 4(c), 403 there are three similar Verilog descriptions using conditional 404 signal assignment to describe hardware. However, the first 405 assignment description would be synthesized as a two-input 406 multiplexer, the second design would be converted into a latch, 407 and the third design would be a tri-state buffer. 408

Fig. 4. Sample exam questions—fundamental knowledge. (a) False path. (b) Setup and hold contraints.

TABLE VI

Exam Result (Spring 2017 Versus Fall 2017)

| Exam Studies<br>/ Weights | Semester           | Grade<br>Av.   | Grade<br>S.D. | Effect<br>size (d) | t                   |

|---------------------------|--------------------|----------------|---------------|--------------------|---------------------|

| Konwledge(40%)            | S 2017  <br>F 2017 | 3.24  <br>3.15 | 0.56          | 0.15               | 0.33  <br>  (p<.05) |

| Skill(60%)                | S 2017  <br>F 2017 | 3.10  <br>3.04 | 0.23          | 0.26               | 0.55<br>  (p<.05)   |

The fourth example in Fig. 4(c) is to test the Verilog coding style. In this case, the combinational design using the "assign" block would be converted into a ten-bit accumulator, and the sequential circuit using the "always" block would be specified as a 10-bit register. Together the design is a ten-bit counter by clock cycles. The design on counters is suggested to separate the combinational and sequential descriptions in order to make the HDL design readable and understandable.

#### 417 B. Exam Results

Final grades are ranked on a scale of 1–5, where 1 is unsat-<sup>419</sup> isfactory, 2 satisfactory, 3 neutral, 4 good, and 5 excellent. The <sup>420</sup> overall student grade of the two-part test is the simple aver-<sup>421</sup> age of the results. Students' background knowledge is assessed <sup>422</sup> based on the results of previously taken courses. *t*-tests show <sup>423</sup> that the initial knowledge of students enrolled the course in <sup>424</sup> Spring 2017 and Fall 2017 is similar as seen in Table VI. The <sup>425</sup> maximum *t* value is 0.55 and the effect size is 0.26.

This article focuses on the comparison between results of students taking the PBL (in Spring 2019) and students not taking the PBL (in Spring 2017 and Fall 2017). The grade average and standard deviation of the exam are shown in the third and fourth columns in Tables VII and VIII. Further, the tai result of *t*-tests is shown in the sixth column.

First, in the second and third rows in Table VII, it shows that the average grades for knowledge testing are 3.24 (S.D. 0.56) and 3.51 (S.D. 0.59), respectively, in Spring 2017 and Spring 2019. There is a 0.27 difference between the two groups of students due to the practical skills achieved by the approach of PBL. The major difference occurs at the test on practical skills

IEEE TRANSACTIONS ON EDUCATION

TABLE VII

Exam Result (Spring 2017 Versus Spring 2019)

| Exam Studies<br>/ Weights | Semester         | Grade<br>Av.   | Grade<br>S.D. | Effect<br>size (d) | t                 |

|---------------------------|------------------|----------------|---------------|--------------------|-------------------|

| Konwledge(40%)            | S 2017<br>S 2019 | 3.24<br>3.51   | 0.56          | 0.47<br>           | 0.96<br>  (p<.05) |

| Skills(60%)               | S 2017<br>S 2019 | 3.10  <br>3.67 | 0.23          | 2.46               | 4.74<br>  (p<.05) |

TABLE VIII

Exam Result (Fall 2017 Versus Spring 2019)

| Exam Studies<br>/ Weights | Semester           | Grade<br>Av. | Grade<br>S.D. | Effect<br>size (d) | t               |

|---------------------------|--------------------|--------------|---------------|--------------------|-----------------|

| Konwledge(40%)            | F 2017 S 2019      | 3.15<br>3.51 | 0.67          | 0.58               | 1.22<br>(p<.05) |

| Skills(60%)               | F 2017  <br>S 2019 | 3.04<br>3.67 | 0.24          | 2.68<br>           | 5.43<br>(p<.05) |

which is shown in the fourth and fifth rows. It can be observed <sup>438</sup> that the average grades for students in Spring 2017 and Spring <sup>439</sup> 2019 are 3.10 (S.D. 0.23) and 3.67 (S.D. 0.24), respectively, <sup>440</sup> showing a significant 0.57 average grade increase between the <sup>441</sup> two groups (p < 0.05) in favor of students that participated in <sup>442</sup> the PBL in Spring 2019. <sup>443</sup>

Likewise, the performance between students in Fall 2017 444 and Spring 2019 is evaluated in Table VIII. It shows similar 445 differences between students participated in the PBL and did 446 not participate. In the knowledge tests, the average grade of 447 students in Fall 2017 is 3.15 (S.D. 0.67) and that of students 448 in Spring 2019 is 3.51 (S.D. 0.59). The significant difference 449 is in the practical skills test. The average grade of students 450 in Fall 2017 is 3.04 (S.D. 0.24), whereas that of students in 451 Spring 2019 is 3.67 (S.D. 0.24), showing a notable difference 452 of 0.63 (p < 0.05). Therefore, it can be stated that the students 453 who worked on the project achieve better results than those 454 who did not (p < 0.05).

According to the *t*-test results, the significance probability  $_{456}$  (*p*-value) is less than the significance level (0.05), indicating  $_{457}$  that there is a statistically significant difference in the results  $_{458}$  between those who participated in the PBL and those who did  $_{459}$  not, particularly to the test on practical skills.  $_{460}$

#### C. Student Survey

A student survey was taken in Spring 2019 to evaluate the 462 PBL effectiveness. In the first column of Table IX, it shows the 463 eight questions to students, and in the first row five answers 464 can be chosen on a scale of A–E, where A is strongly agree, B 465 is agree, C is unsure, D is disagree, and E is strongly disagree. 466

Specifically, for the first question, 84.62% students strongly 467 agree that the course design is helpful to bridge the gap between 468 academy and industry needs. For the second and third questions, 469 61.54% and 84.62% students strongly agree that the lectures 470 and training are helpful to the final project. Additionally, for 471 the fourth and fifth questions, more than 75% students strongly 472

461

| TABLE IX       |

|----------------|

| STUDENT SURVEY |

| Survey Questions                                                                                                                                               | A<br>(Strongly<br>agree) | B<br>(Agree) | C<br>(Unsure) | D<br>(Disagree) | E<br>(Strongly<br>Disagree) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------|---------------|-----------------|-----------------------------|

| Q1: Overall, do you think the design of the class is helpful to bridge the gap between academy and industry needs in integrated circuit design?                | 84.62%                   | 15.38%       | 0             | 0               | 0                           |

| Q2: Do you think the five-week lecture is helpful to know about the latest technologies to carry out the final project?                                        | 61.54%                   | 38.46%       | 0             | 0               | 0                           |

| Q3: Do you think the two-lecture training with the integrated circuit design flow, EDA tools, simulation environment is helpful to the final project?          | 84.62%                   | 15.38%       | 0             | 0               | 0                           |

| Q4: Did the project work, including the IP tree and system-on-chip (SoC) tree, help you understand and learn the basics of design and implementation of a SoC? | 76.92                    | 23.08        | X             |                 |                             |

| Q5: Did the Project-Based Learning (PBL) during the class help your understanding the industrial FPGA design flow?                                             | 84.62%                   | 15.38%       | 0             | 0               | 0                           |

| Q6: Did you find the final project interesting?                                                                                                                | 92.30%                   | 7.70%        | 0             | 0               | 0                           |

| Q7: Did the project help you to extend your multidisciplinary knowledge?                                                                                       | 61.54%                   | 38.46%       | 0             | 0               | 0                           |

| Q8: Was the project work easy to finish?                                                                                                                       | 23.08%                   | 30.77%       | 23.08%        | 15.38%          | 7.70%                       |

473 agree that the project is helpful to understand the FPGA design 474 flow. For the sixth question, 92.3% students strongly found 475 the project interesting, and for the seventh question, 61.54% 476 students strongly agree that the project helps them to extend 477 their multidisciplinary knowledge. The objective of the PBL 478 is to make less than 25% students feel neither too easy nor 479 too hard to complete the project. For the last question, it can 480 be observed that the difficulty of the project is appropriate to 481 graduate student in a semester-long course.

## 482 D. Student Evaluation to Academic Abilities

In this section, the difference between the courses over the three semesters are discussed. In general, the teaching matetas rials, assignments, and exams are equally performed through the three semesters. In Spring 2019, however, a major project tas added and executed spanning over eight weeks to carry out the entire FPGA design flow.

At the end of each semester, students evaluate the course 489 490 including the difficulty of the course and the level of 491 knowledge/understanding gained from the course. As shown <sup>492</sup> in the second to the fourth rows in Table X, 38% students <sup>493</sup> in Spring 2019 feel that the course is hard due to the addi-494 tional work to the project, comparing to 29% and 25% students 495 in Fall 2017 and Spring 2017. Though it is the most diffi-496 cult semester, 92% students in Spring 2019 rate the level of 497 knowledge/understanding gained from this course to be high as shown in the sixth row, compared to the percentage of 86% 498 and 90% students in the Fall 2017 and Spring 2017. It is a solid 499 <sup>500</sup> evidence to demonstrate that the improvement of the course <sup>501</sup> is principally due to the PBL learning industrial flow.

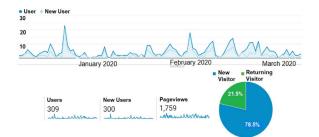

#### 502 E. Google Analytics Results

In order to serve researchers, engineers, and students in IC design field, the project has been made publicly available on https://sceweb.sce.uhcl.edu/xiaokun/OpenIC/ since December 2019. As the results on Google Analytics [14], shown in Fig. 5, the open-source Web page has resulted in 300 new users and 1759 page views until March 2020. It has been widely browsed

TABLE X STUDENT EVALUATION TO THE KNOWLEDGE/UNDERSTANDING GAINED FROM THE COURSE

|   |                                                                                                  | /    |             |      |        |

|---|--------------------------------------------------------------------------------------------------|------|-------------|------|--------|

|   | Compared to my                                                                                   | Hard | As expected | Easy |        |

|   | expectations, this<br>course was                                                                 | 38%  | 62%         | 0    | S 2019 |

|   |                                                                                                  | 29%  | 71%         | 0    | F 2017 |

|   |                                                                                                  | 25%  | 60%         | 15%  | S 2017 |

| Ī | How would you rate<br>the level of knowledge<br>or understanding you<br>gained from this course? | High | Adequate    | Low  |        |

|   |                                                                                                  | 92%  | 8%          | 0    | S 2019 |

|   |                                                                                                  | 86%  | 14%         | 0    | F 2017 |

|   |                                                                                                  | 90%  | 10%         | 0    | S 2017 |

Fig. 5. Results from Google Analytics.

and downloaded from users in more than 20 countries during 509 the last three months. The preliminary result demonstrates that 510 this project has a potential to be widely used in teaching many 511 advanced level courses in the future, such as advanced digital 512 system design, verification methodology, FPGA design and 513 verification, and many more. 514

#### VIII. CONCLUSION 515

In academia, to provide engineering students opportunities 516 to engage with industry-relevant projects is a big challenge due 517 to a lack of research to the real-world requirements in industry 518 and the time constraint to set up a similar design environment to industry counterparts. Therefore, this article presents 520 521 a PBL approach by using an open source platform, targeted <sub>522</sub> at covering basic qualifications for industry needs in the field 523 of IC design. The project is appropriate for graduate students computer engineering program. It provides an opportunity 524 in discuss and solve practical IC design problems, work in 525 to 526 teams, and achieve a joint result by PBL. The exam results show significantly better grades for students who participated 527 the project. More important, the presented PBL platform is 528 in 529 made publicly available, offering a good framework to imple-530 ment practical courses related to the multidisciplinary field of 531 computer engineering and improve students' knowledge and 532 skills in topics of computer architecture, digital circuit/system 533 design, embedded system, etc.

# 534 A. Future Work

Recently, online learning platforms and open source projects 535 536 are becoming increasingly popular for teaching and manag-537 ing engineering courses [23], [24]. For example, Rodriguez-Sanchez et al. [23] presented some international collaborative 538 projects that students online from Indian and Spanish are able 539 540 to work together with open source tools. Similarly, in [24], <sup>541</sup> new approaches with e-learning material, including Web-based 542 animations, lecture videos, tools for graphical simulation, and remote labs, were developed and described in the literature. 543 Under this context, future work of this article will focus 544 on creating a network laboratory with online-available plat-545 546 forms and tools, as well as effective remote communication and teamwork. For example, the Amazon Elastic Compute 547 548 Cloud (Amazon EC2) can be used to develop FPGA applica-<sup>549</sup> tions with Amazon Web Services (AWS) cloud [26], and many 550 free-registration platforms like FPGA Accelerator Research <sup>551</sup> Infrastructure Cloud (FAbRIC) [27] and open-source projects 552 and tools on Github.com like Digital simulator [25] can be 553 used to expand the online platform.

#### 554

#### REFERENCES

- D. Tsybulsky and Y. Muchnik-Rozanov, "The development of student-teachers' professional identity while team-teaching science classes using a project-based learning approach: A multi-level analysis," *Teach. Teach. Educ.* vol. 79, pp. 48–59, Mar. 2019.

- J. Larson, S. S. Jordan, M. Lande, and S. Weiner, "Supporting self-directed learning in a project-based embedded systems design course," *IEEE Trans. Educ.*, vol. 63, no. 2, pp. 88–97, May 2020.

- [3] K. D. Pham, M. Vesper, D. Koch, and E. Hung, "EFCAD—An embedded FPGA CAD tool flow for enabling on-chip self-compilation," in *Proc. IEEE 27th Annu. Int. Symp. Field-Program. Custom Comput. Mach. (FCCM)*, San Diego, CA, USA, Jun. 2019, pp. 5–8.

- Mach. (FCCM), San Diego, CA, USA, Jun. 2019, pp. 5–8.

M. Mykhailova and K. M. Svore, "Teaching quantum computing through a practical software-driven approach: Experience report," in *Proc. 51st ACM Techn. Symp. Comput. Sci. Educ. (SIGCSE)*, Feb. 2020, pp. 1019–1025.

- [5] N. A. M. Salleh and K. M. Yusof, "Industrial based final year engineering projects: Problem based learning (PBL)," in *Proc. 7th World Eng. Educ. Forum (WEEF)*, Kuala Lumpur, Malaysia, Sep. 2018, pp. 782–786.

- 574 [6] Synopsys Electronic Design University Program. Accessed: Apr. 18,

575 2019. [Online]. Available: https://www.synopsys.com/community/

576 university-program

- [7] Cadence University Software Programs. Accessed: Apr. 18, 2019.

[78] [Online]. Available: https://ip.cadence.com/about/university-program

- [8] Mentor Graphics Higher Education Program. Accessed: Apr. 18, 2019.

[Online]. Available: https://www.mentor.com/company/higher\_ed

- [9] Xilinx University Program. Accessed: Apr. 18, 2019. [Online]. Available: https://www.xilinx.com/support/university.html

- [10] Intel FPGA University Program. Accessed: Apr. 18, 2019. [Online]. 583 Available: https://software.intel.com/en-us/fpga-academic 584

- [11] M. Božanić and S. Sinha, "A survey of current trends in master's 585 programs in microelectronics," *IEEE Trans. Educ.*, vol. 61, no. 2, 586 pp. 151–157, May 2018. 587

- X. Yang, Y. Zhang, and L. Wu, "A scalable image/video processing platform with open source design and verification environment," in *Proc. 20th Int. Symp. Qual. Electron. Design (ISQED)*, Santa Clara, 590 CA, USA, Apr. 2019, pp. 110–116.

- Y. Zhang, X. Yang, L. Wu, and J. H. Andrian, "A case study on approximate FPGA design with an open-source image processing platform," 593 in *Proc. IEEE Comput. Soc. Annu. Symp. VLSI (ISVLSI)*, Miami, FL, 594 USA, Sep. 2019, pp. 372–377. 595

- M. Yamba-Yugsi, S. Luján-Mora, and H. Pacheco-Romero, "Using 596 Google analytics to analyze users of a massive open online course," 597 in *Proc. Int. Conf. Inf. Syst. Comput. Sci. (INCISCOS)*, Quito, Ecuador, 598 Apr. 2020, pp. 280–285.

- [15] D. Oguz and K. Oguz, "Perspectives on the gap between the software 600 industry and the software engineering education," *IEEE Access*, vol. 7, 601 pp. 117527–117543, 2019.

- [16] D. Akdur, "The design of a survey on bridging the gap between software industry expectations and academia," in *Proc. 8th Mediterr. Conf.* 604 *Embedded Comput/(MECO)*, Budva, Montenegro, Jul. 2019, pp. 1–5. 605

- [17] M. C. Rodriguez-Sanchez, A. Torrado-Carvajal, J. Vaquero, 606 S. Borromeo, and J. A. Hernandez-Tamames, "An embedded systems 607 course for engineering students using open-source platforms in wireless 608 scenarios," *IEEE Trans. Educ.*, vol. 59, no. 4, pp. 248–254, Nov. 2016. 609

- [18] L. Albasha and O. Hammi, "Introducing industrial design flow of an 610 RFIC chip to a graduate course: Building the ecosystem and bridging 611 the gap between industry and academia," *IET Circuits Devices Syst.*, 612 vol. 11, no. 4, pp. 299–303, Jul. 2017.

- T. Wu, Y. Wang, W. Shi, and J. Lu, "HydraMini: An FPGA-based affordable research and education platform for autonomous driving," in *Proc. Int. Conf. Connected Auton. Driving (MetroCAD)*, Detroit, MI, USA, 616 Jul. 2020, pp. 45–52.

- [20] T. McGrew and E. Schonauer, "Framework and tools for undergraduates designing RISC-V processors on an FPGA in computer architecture education," in *Proc. Int. Conf. Comput. Sci. Comput. Intell. (CSCI)*, Las Vegas, NV, USA, Apr. 2019, pp. 778–781.

- [21] L. Shanshan and Y. Shiqiang, "Digital logic experiment teaching based on experimental platform," in *Proc. 12th Int. Conf. Comput. Sci. Educ.* 623 (*ICCSE*), Houston, TX, USA, Oct. 2017, pp. 33–37. 624

- [22] J. Durre and H. Blume, "SF<sup>3</sup>: A scalable and flexible FPGAframework for education and rapid prototyping," in *Proc. IEEE Int. Conf.* 626 *Microelectron. Syst. Educ. (MSE)*, Jun. 2017, pp. 35–38. 627

- [23] M. C. Rodriguez-Sanchez, P. Chakraborty, and N. Malpica, 628 "International collaborative projects on digital electronic systems 629 using open source tools," *Comput. Appl. Eng. Educ.*, vol. 28, no. 4, 630 pp. 792–802, Jul. 2020. 631

- [24] M. Winzker and A. Schwandt, "Open education teaching unit for lowpower design and FPGA image processing," in *Proc. IEEE Front. Educ.* 633 *Conf. (FIE)*, Covington, KY, USA, Mar. 2020, pp. 1–9. 634

- [25] H. Neemann. (2014). Digital. [Online]. Available: https://github.com/ hneemann

- [26] (2020). Amazon EC2. [Online]. Available: https://docs.aws.amazon.com/ 637 AWSEC2/latest/UserGuide/concepts.html 638

- [27] (2018). FPGA Accelerator Research Infrastructure Cloud (FAbRIC).

[0nline]. Available: https://wikis.utexas.edu/display/fabric/Home

Xiaokun Yang (Member, IEEE) received the Ph.D. degree from the 641 Department of Electrical and Computer Engineering, Florida International 642 University, Miami, FL, USA, in Spring 2016. 643

From 2007 to 2012, he has worked as an ASIC Design and Verification 644 Engineer with Advanced Micro Devices, China Electronic Corporation, and 645 PowerLayer MicroSystems, Beijing, China. He has more than 15 years of 646 experience in integrated circuit design and verification. He is currently an 647 Assistant Professor with the College of Science and Engineering, University 648 of Houston-Clear Lake, Houston, TX, USA. As the first author and cor-649 responding author, he has published more than 50 papers, including three 650 patents, more than 15 peer-review journals, and more than 30 prestigious 651 international conferences. His research interests include HW/SW co-design 652 on FPGA, FPGA acceleration on AI/ML, and system-on-chip architecture. 653

Dr. Yang has served on several editorial boards and journal reviewers, including the IEEE TRANSACTIONS ON COMPUTERS, the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, 656 and the IEEE TRANSACTIONS ON EDUCATION, and numerous conference committees and section chairs, such as ISVLSI and ISQED. 658